## **arm** Education Media

## Modern System-on-Chip Design on Arm

**TEXTBOOK**

David J. Greaves

SoC Design

# Modern System-on-Chip Design on Arm

# Modern System-on-Chip Design on Arm

**DAVID J. GREAVES**

Arm Education Media is an imprint of Arm Limited, 110 Fulbourn Road, Cambridge, CBI 9NJ, UK

Copyright © 2021 Arm Limited (or its affiliates). All rights reserved.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording or any other information storage and retrieval system, without permission in writing from the publisher, except under the following conditions:

#### Permissions

- You may download this book in PDF format from the Arm.com website for personal, non-commercial use only.

- You may reprint or republish portions of the text for non-commercial, educational or research purposes but only if there is an attribution to Arm Education.

This book and the individual contributions contained in it are protected under copyright by the Publisher (other than as may be noted herein).

#### Notices

Knowledge and best practice in this field are constantly changing. As new research and experience broaden our understanding, changes in research methods and professional practices may become necessary.

Readers must always rely on their own experience and knowledge in evaluating and using any information, methods, project work, or experiments described herein. In using such information or methods, they should be mindful of their safety and the safety of others, including parties for whom they have a professional responsibility.

To the fullest extent permitted by law, the publisher and the authors, contributors, and editors shall not have any responsibility or liability for any losses, liabilities, claims, damages, costs or expenses resulting from or suffered in connection with the use of the information and materials set out in this textbook.

Such information and materials are protected by intellectual property rights around the world and are copyright © Arm Limited (or its affiliates). All rights are reserved. Any source code, models or other materials set out in this reference book should only be used for non-commercial, educational purposes (and/or subject to the terms of any license that is specified or otherwise provided by Arm). In no event shall purchasing this textbook be construed as granting a license to use any other Arm technology or know-how.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. For more information about Arm's trademarks, please visit https://www.arm.com/company/policies/trademarks.

Arm is committed to making the language we use inclusive, meaningful, and respectful. Our goal is to remove and replace non-inclusive language from our vocabulary to reflect our values and represent our global ecosystem.

Arm is working actively with our partners, standards bodies, and the wider ecosystem to adopt a consistent approach to the use of inclusive language and to eradicate and replace offensive terms. We recognise that this will take time. This book contains references to non-inclusive language; it will be updated with newer terms as those terms are agreed and ratified with the wider community.

Contact us at education@arm.com with questions or comments about this course. You can also report non-inclusive and offensive terminology usage in Arm content at terms@arm.com.

ISBN: 978-1-911531-37-1

978-1-911531-38-8 (ePub) 978-1-911531-36-4 (print)

Version: ePDF

For information on all Arm Education Media publications, visit our website at https://www.arm.com/resources/education/books

To report errors or send feedback, please email edumedia@arm.com

|    | Prefa  | xvii                   |                                                 |        |

|----|--------|------------------------|-------------------------------------------------|--------|

|    | Ackn   | owledgm                | ents                                            | xix    |

|    | Auth   | or Biogra <sub>l</sub> | phy                                             | xxi    |

|    | List o | of Figures             |                                                 | xxiii  |

|    | List o | of Tables              |                                                 | xxxvii |

| 1. | Intro  | oduction               | to System-on-Chip                               |        |

|    | 1.1    | What is                | s a System-on-Chip?                             | 2      |

|    |        | 1.1.1                  | Historical Review                               | 2      |

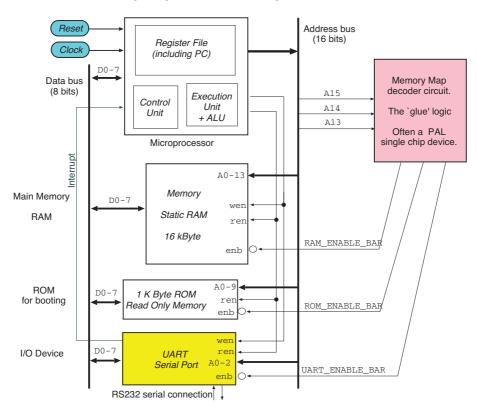

|    |        | 1.1.2                  | Simple Microprocessor Net-level Connections     | 4      |

|    |        | 1.1.3                  | Full Netlist and Memory Map for a Microcomputer | 5      |

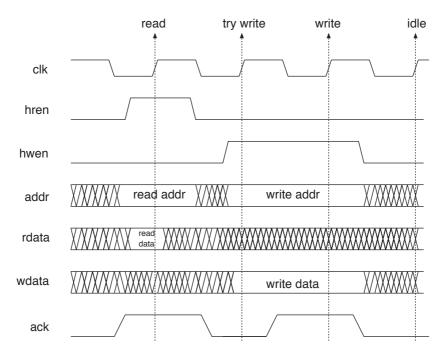

|    |        | 1.1.4                  | Separate Read and Write Data Busses             | 7      |

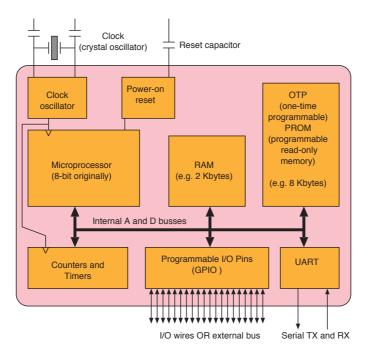

|    | 1.2    | Microc                 | controllers                                     | 8      |

|    | 1.3    | Later C                | Chapters                                        | 10     |

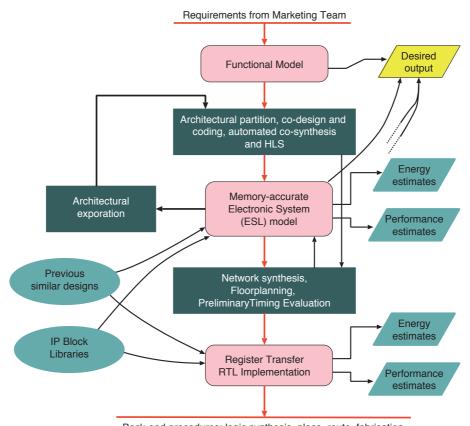

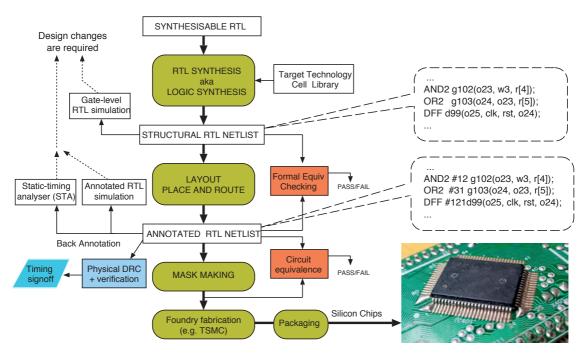

|    | 1.4    | SoC De                 | esign Flows                                     | 11     |

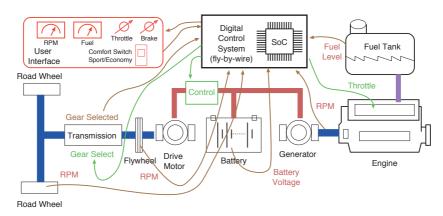

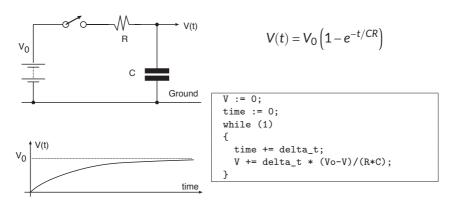

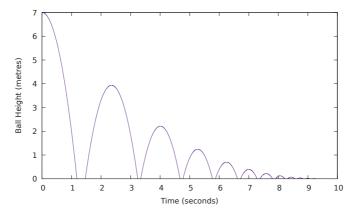

|    |        | 1.4.1                  | Functional Model                                | 11     |

|    |        | 1.4.2                  | Architectural Partition                         | 14     |

|    |        | 1.4.3                  | Architectural Partition and Co-design           | 15     |

|    |        | 1.4.4                  | IP Blocks                                       | 16     |

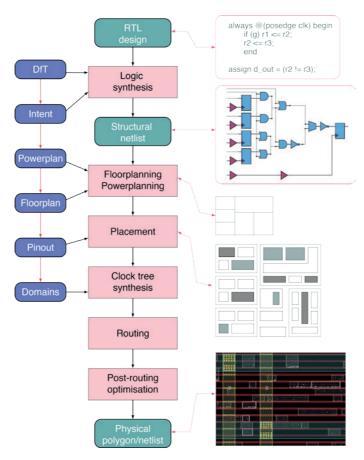

|    |        | 1.4.5                  | Synthesis                                       | 17     |

|    |        | 1.4.6                  | Simulation                                      | 17     |

|    |        | 1.4.7                  | Back-end Flow                                   | 18     |

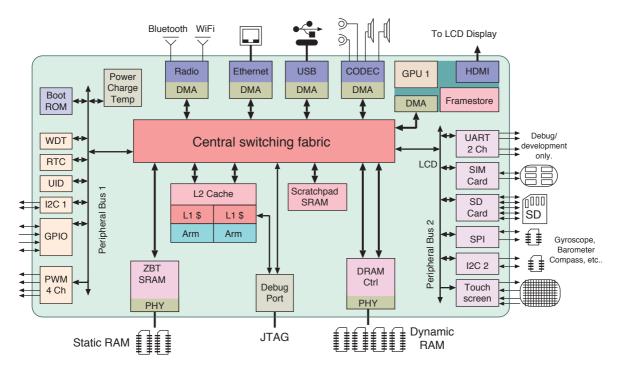

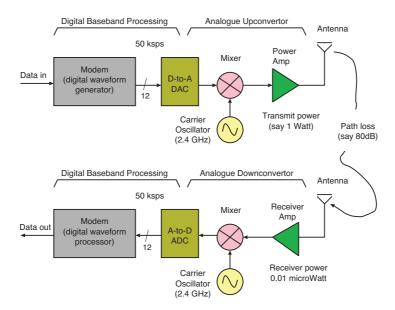

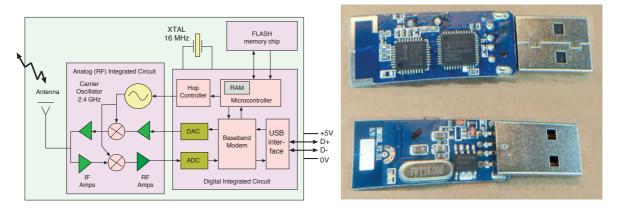

|    |        | 1.4.8                  | Example: A Cell Phone                           | 20     |

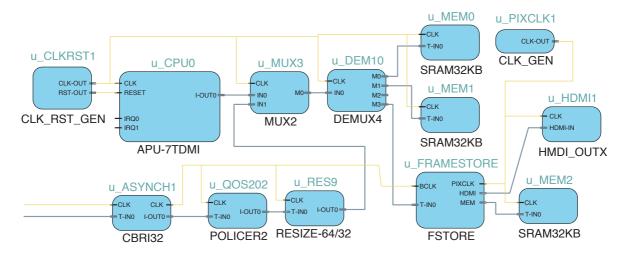

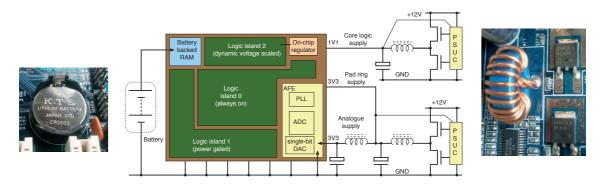

|    |        | 1.4.9                  | SoC Example: Helium 210                         | 21     |

|    | 1.5    | SoC Te                 | chnology                                        | 24     |

|    | 1.6    | Summa                  | ary                                             | 26     |

|    |        | 1.6.1                  | Exercises                                       | 26     |

| 2.1 |          | lemory and IP Blocks for Cores                     | 28 |

|-----|----------|----------------------------------------------------|----|

|     | 2.1.1    | ISAs                                               | 30 |

|     | 2.1.2    | Vector Instructions                                | 31 |

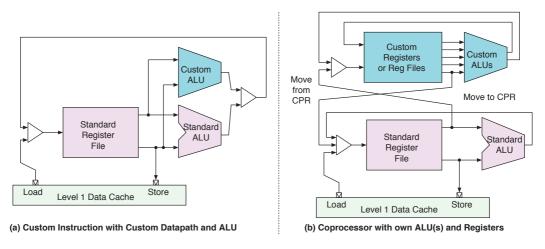

|     | 2.1.3    | Custom Instructions                                | 32 |

|     | 2.1.4    | The Classic Five-stage Pipeline                    | 32 |

| 2.2 | Super-s  | calar Processors                                   | 33 |

|     | 2.2.1    | Virtual Memory Management Units: MMU and IOMMU     | 36 |

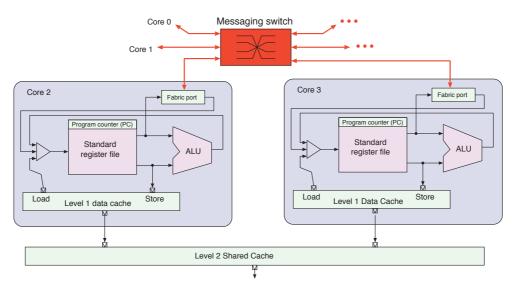

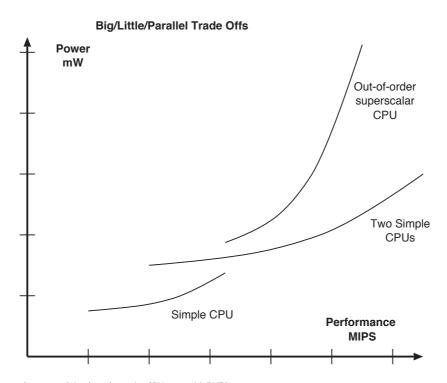

| 2.3 | Multi-co | ore Processing                                     | 37 |

|     | 2.3.1    | Simultaneous Multithreading                        | 39 |

| 2.4 | Cache E  | Design                                             | 39 |

|     | 2.4.1    | Snooping and Other Coherency Protocols             | 43 |

| 2.5 | Interru  | pts and the Interrupt Controller                   | 46 |

|     | 2.5.1    | Interrupt Structure Within a Device                | 47 |

| 2.6 | Memor    | y Technology                                       | 48 |

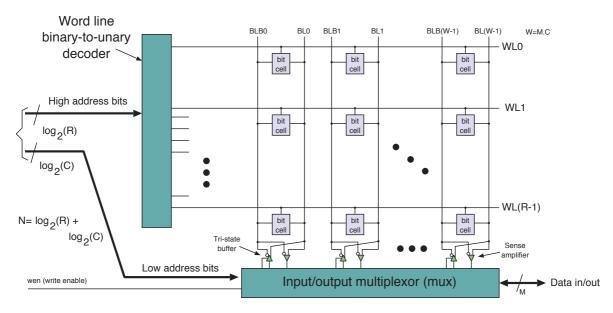

|     | 2.6.1    | Logical and Physical Layouts                       | 49 |

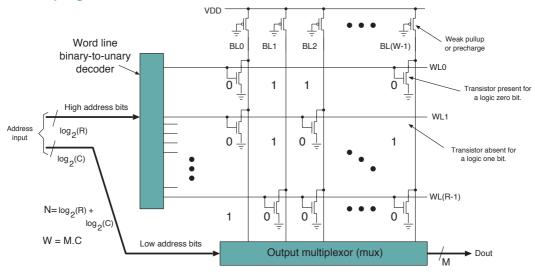

|     | 2.6.2    | Mask-programmed ROM                                | 51 |

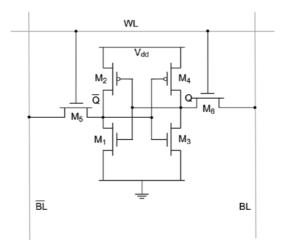

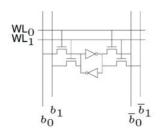

|     | 2.6.3    | Static Random Access Memory                        | 52 |

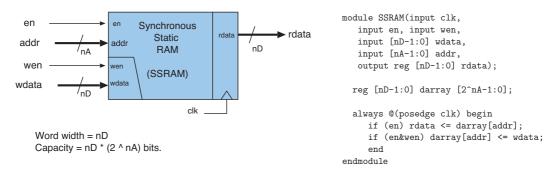

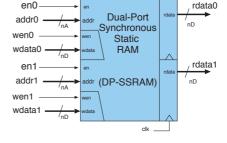

|     | 2.6.4    | Synchronous Static RAM                             | 53 |

|     | 2.6.5    | Dual-ported Static RAM                             | 54 |

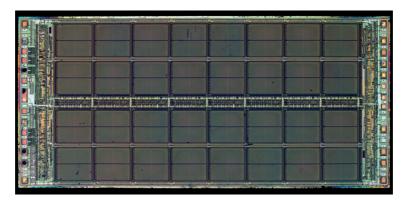

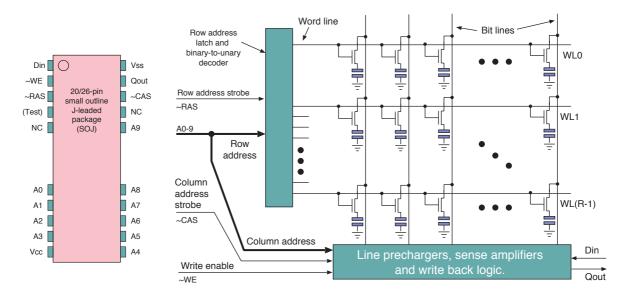

|     | 2.6.6    | Dynamic RAM                                        | 54 |

|     | 2.6.7    | Electrically Alterable ROMs                        | 59 |

|     | 2.6.8    | Floating-gate EA-ROMs and Flash                    | 61 |

|     | 2.6.9    | Emerging Memory Technologies                       | 62 |

|     | 2.6.10   | Processor Speed versus Memory Speed                | 63 |

| 2.7 | SoC I/O  | Blocks                                             | 64 |

|     | 2.7.1    | Universal Asynchronous Receiver-Transmitter (UART) | 65 |

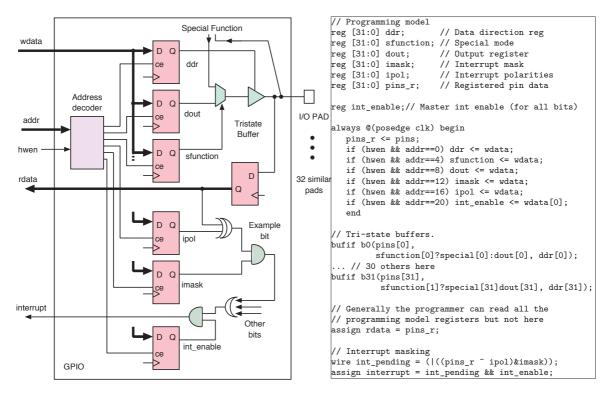

|     | 2.7.2    | Parallel Ports Using General-purpose I/O           | 68 |

|     | 2.7.3    | General-purpose Input/Output Pins                  | 69 |

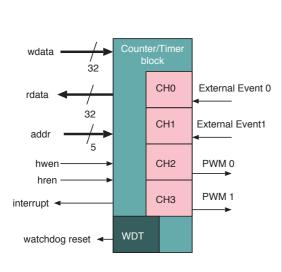

|     | 2.7.4    | Counter/Timer Blocks                               | 70 |

3.4.5

AMBA 5 CHI

124

|    | 3.5   | Advanc              | ed Interconnect Topologies                    | 126 |

|----|-------|---------------------|-----------------------------------------------|-----|

|    |       | 3.5.1               | Traffic Flow Matrix                           | 127 |

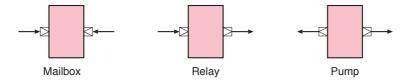

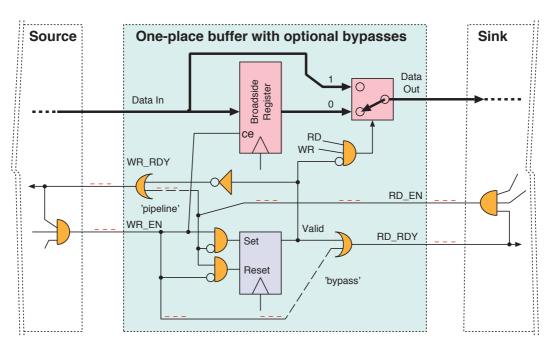

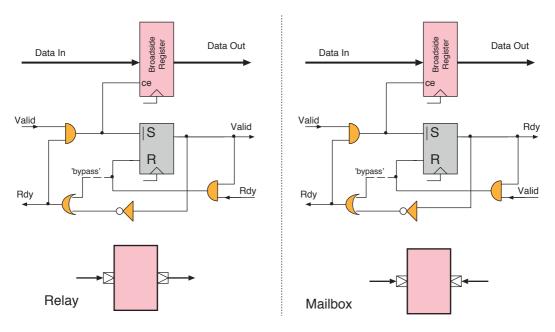

|    | 3.6   | Interco             | nnect Building Blocks                         | 133 |

|    | 3.7   | Long-di             | istance Interconnects                         | 136 |

|    |       | 3.7.1               | Domain Crossing                               | 136 |

|    |       | 3.7.2               | Metastability Theory                          | 137 |

|    |       | 3.7.3               | CD-crossing Bridge                            | 138 |

|    |       | 3.7.4               | Harmonic Clocks                               | 139 |

|    |       | 3.7.5               | PD Crossing                                   | 141 |

|    | 3.8   | Serialis            | er and Deserialiser: SERDES                   | 142 |

|    |       | 3.8.1               | PCIe and SATA                                 | 144 |

|    |       | 3.8.2               | CCIX, CXL and NVLink                          | 144 |

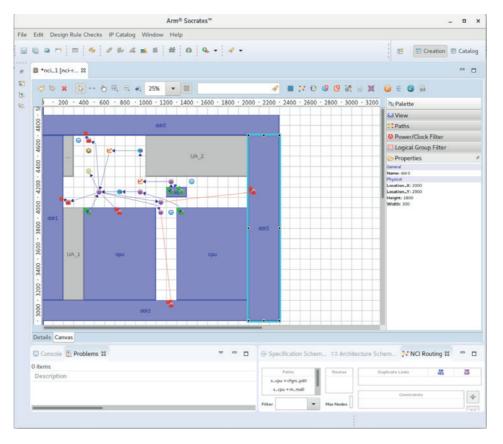

|    | 3.9   | Automa              | atic Topology Synthesis                       | 145 |

|    |       | 3.9.1               | Domain Assignment                             | 145 |

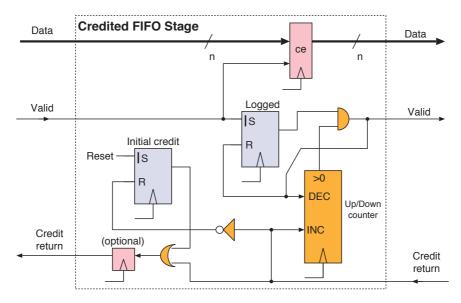

|    |       | 3.9.2               | FIFO Buffer Sizing                            | 146 |

|    |       | 3.9.3               | Link Sizing                                   | 147 |

|    | 3.10  | Summa               | ary                                           | 147 |

|    |       | 3.10.1              | Exercises                                     | 148 |

| 4. | Syste | em Desig            | n Considerations                              |     |

|    | 4.1   | Design              | Objectives and Metrics                        | 154 |

|    | 4.2   | Parallel            | Speedup Theory                                | 156 |

|    |       | 4.2.1               | Contention and Arbitration                    | 157 |

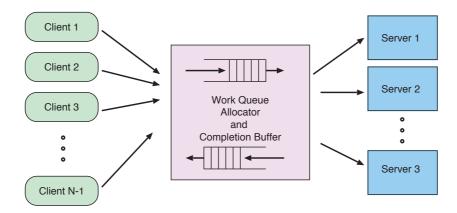

|    | 4.3   | FIFO Q              | ueuing Theory and QoS                         | 159 |

|    |       | 4.3.1               | Classical Single-server and Open Queue Models | 160 |

|    |       | 4.3.2               | Expedited Service Queuing                     | 163 |

|    |       | 4.3.3               | Statistical Multiplexing Gain                 | 164 |

|    |       | 4.3.4               | QoS Policing                                  | 166 |

|    | 4.4   | Design <sup>1</sup> | Trade-offs                                    | 168 |

|    |       | 4.4.1               | Thermal Design                                | 169 |

|    |       | 4.4.2               | Folding, Re-timing and Recoding               | 171 |

|    |       |                     |                                               |     |

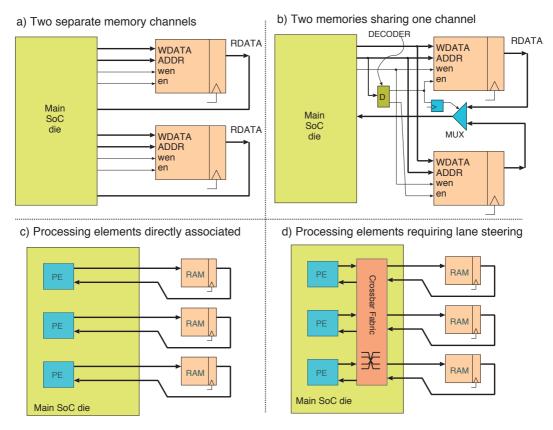

| 4.5  | Design Trade-offs in Memory Systems |                                                                                                                           | 175 |

|------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|

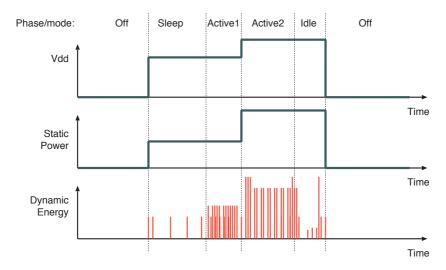

| 4.6  | SoC Ene                             | ergy Minimisation                                                                                                         | 182 |

|      | 4.6.1                               | Power, Resistance and Capacitance                                                                                         | 182 |

|      | 4.6.2                               | Dynamic Energy and Dynamic Power                                                                                          | 183 |

|      | 4.6.3                               | Static Power Use                                                                                                          | 185 |

|      | 4.6.4                               | Wiring and Capacitance Modelling                                                                                          | 186 |

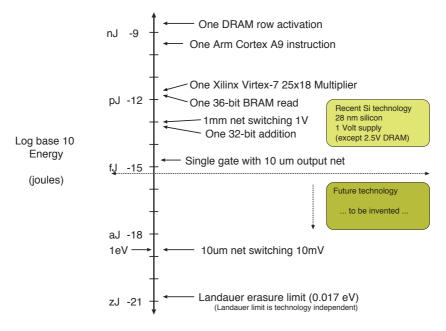

|      | 4.6.5                               | Landauer Limit and Reversible Computation                                                                                 | 188 |

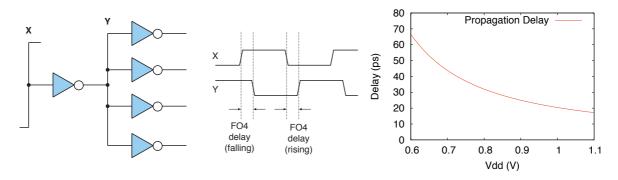

|      | 4.6.6                               | Gate Delay as a Function of Supply Voltage                                                                                | 190 |

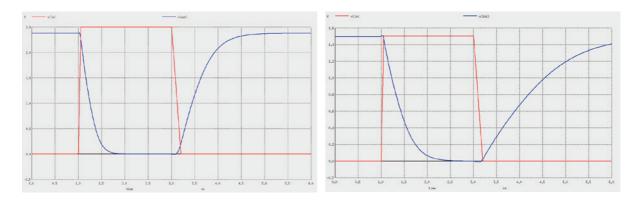

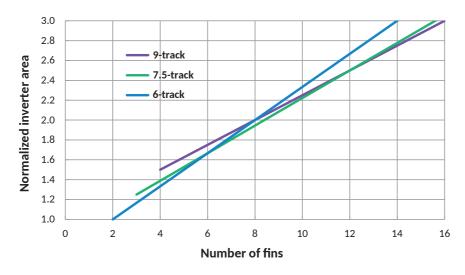

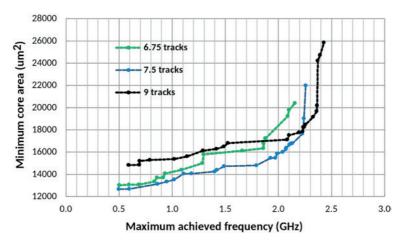

|      | 4.6.7                               | SPICE Simulation of an Invertor                                                                                           | 191 |

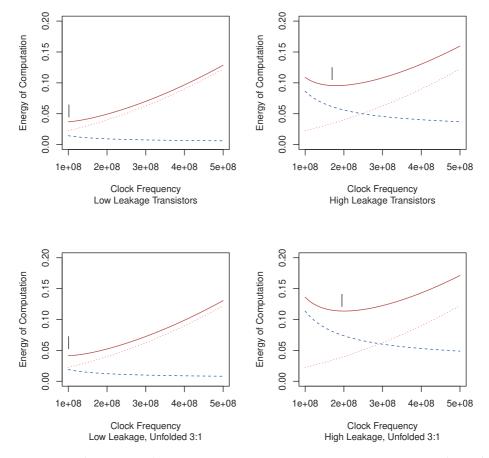

|      | 4.6.8                               | Dynamic Voltage and Frequency Scaling                                                                                     | 191 |

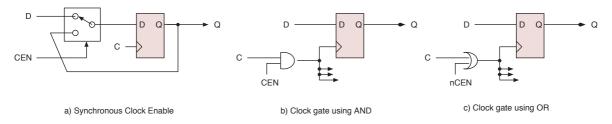

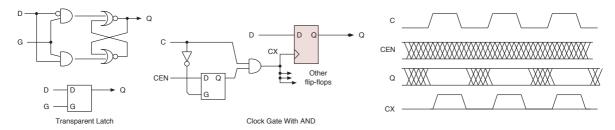

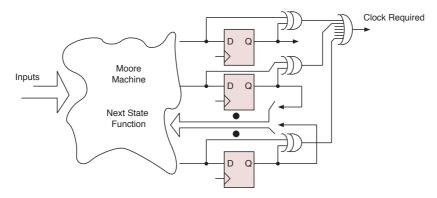

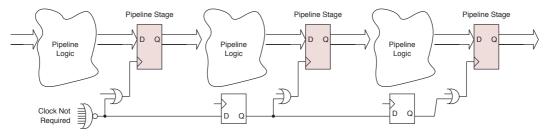

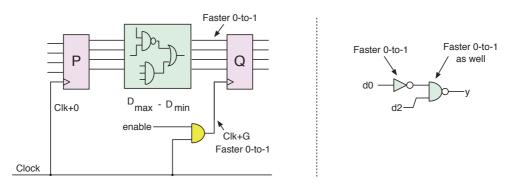

|      | 4.6.9                               | Dynamic Clock Gating                                                                                                      | 194 |

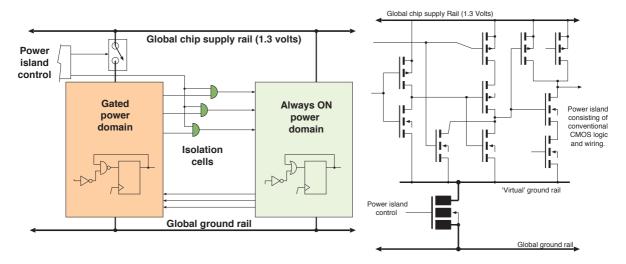

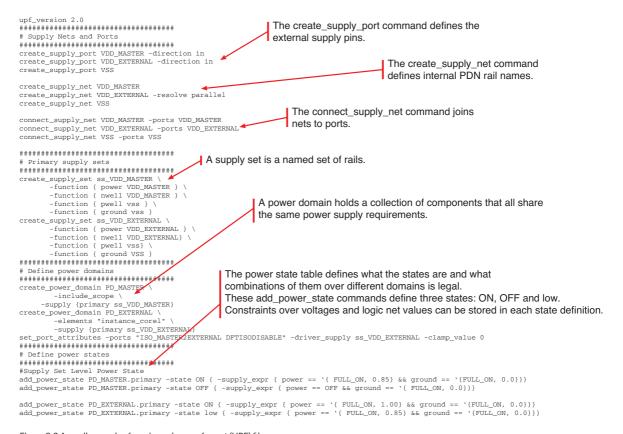

|      | 4.6.10                              | Dynamic Supply Gating                                                                                                     | 196 |

|      | 4.6.11                              | Future Trends for Energy Use                                                                                              | 199 |

| 4.7  | Designi                             | ng for Testability and Debug Integration                                                                                  | 200 |

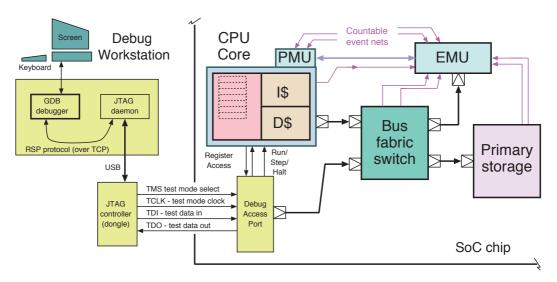

|      | 4.7.1                               | Application Debugging                                                                                                     | 200 |

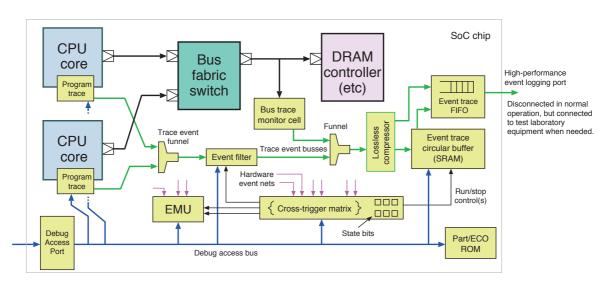

|      | 4.7.2                               | Multi-core Debug Integration                                                                                              | 202 |

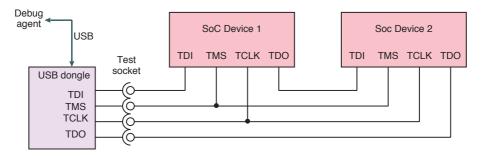

|      | 4.7.3                               | Debug Navigation and JTAG                                                                                                 | 204 |

|      | 4.7.4                               | Additional DAP Facilities                                                                                                 | 205 |

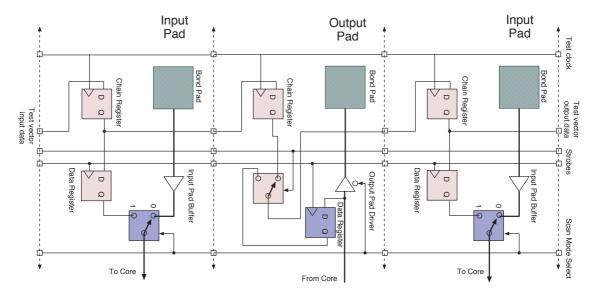

|      | 4.7.5                               | Boundary and General Path Scans                                                                                           | 206 |

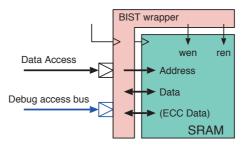

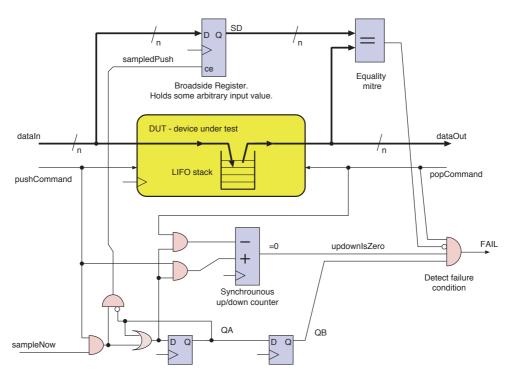

|      | 4.7.6                               | BIST for SRAM Memories (MBIST)                                                                                            | 207 |

| 4.8  | Reliabil                            | ity and Security                                                                                                          | 208 |

|      | 4.8.1                               | Physical Faults, Performance Degradation, Error Detection and Correction, and Pre- and Post-silicon Mitigation Techniques | 208 |

| 4.9  | Hardwa                              | are-based Security                                                                                                        | 209 |

|      | 4.9.1                               | Trusted Platform and Computer Modules                                                                                     | 210 |

|      | 4.9.2                               | Trusted Execution Mode                                                                                                    | 211 |

|      | 4.9.3                               | Capability-based Protection                                                                                               | 211 |

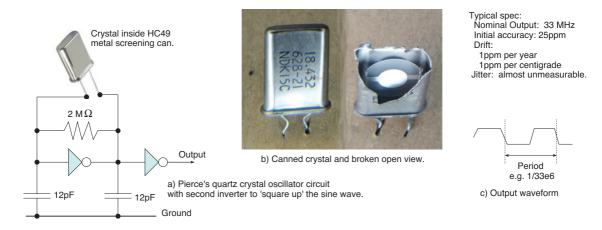

|      | 4.9.4                               | Clock Sources                                                                                                             | 211 |

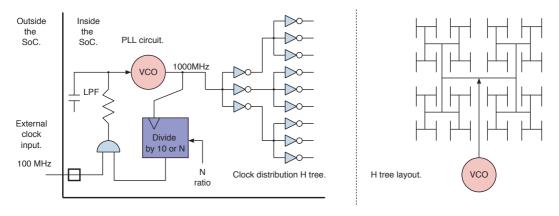

|      | 4.9.5                               | PLL and Clock Trees                                                                                                       | 212 |

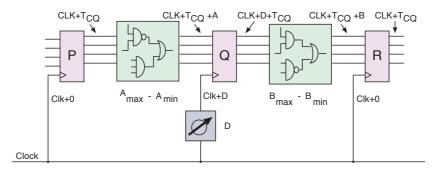

|      | 4.9.6                               | Clock Skewing and Multi-cycle Paths                                                                                       | 213 |

| 4.10 | Summa                               | ry                                                                                                                        | 216 |

|      | 4.10.1                              | Exercises                                                                                                                 | 216 |

| 5. | Elec | Electronic System-Level Modelling |                                                             |     |  |  |  |

|----|------|-----------------------------------|-------------------------------------------------------------|-----|--|--|--|

|    | 5.1  | Modell                            | ling Abstractions                                           | 220 |  |  |  |

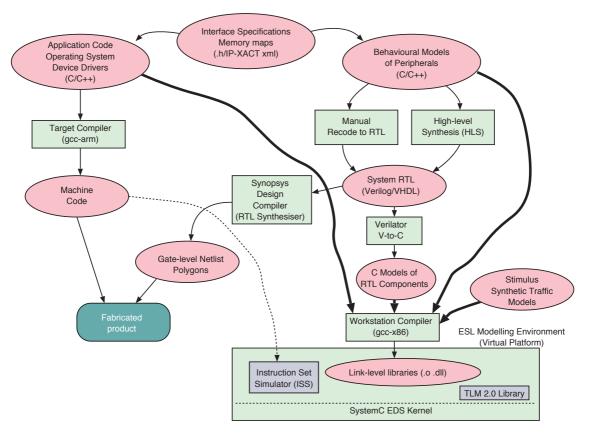

|    |      | 5.1.1                             | ESL Flow Diagram                                            | 223 |  |  |  |

|    | 5.2  | Interco                           | onnect Modelling                                            | 225 |  |  |  |

|    |      | 5.2.1                             | Stochastic Interconnect Modelling                           | 226 |  |  |  |

|    |      | 5.2.2                             | Cycle-accurate Interconnect Modelling                       | 226 |  |  |  |

|    | 5.3  | System                            | nC Modelling Library                                        | 227 |  |  |  |

|    |      | 5.3.1                             | SystemC Structural Netlist                                  | 229 |  |  |  |

|    |      | 5.3.2                             | SystemC Threads and Methods                                 | 230 |  |  |  |

|    |      | 5.3.3                             | SystemC Plotting and its GUI                                | 232 |  |  |  |

|    |      | 5.3.4                             | Towards Greater Modelling Efficiency                        | 233 |  |  |  |

|    | 5.4  | Transa                            | ction-level Modelling                                       | 234 |  |  |  |

|    |      | 5.4.1                             | OSCI TLM 1.0 Standard                                       | 235 |  |  |  |

|    |      | 5.4.2                             | OSCI TLM 2.0 Standard                                       | 237 |  |  |  |

|    |      | 5.4.3                             | TLM Models with Timing (TLM+T)                              | 241 |  |  |  |

|    |      | 5.4.4                             | TLM with Loosely Timed Modelling                            | 241 |  |  |  |

|    |      | 5.4.5                             | Modelling Contention Under Loosely Timed TLM                | 244 |  |  |  |

|    |      | 5.4.6                             | Non-blocking TLM coding                                     | 245 |  |  |  |

|    |      | 5.4.7                             | Typical ISS Setup with Loose Timing and Temporal Decoupling | 246 |  |  |  |

|    |      | 5.4.8                             | TLM Transactors for Bridging Modelling Styles               | 246 |  |  |  |

|    |      | 5.4.9                             | ESL Model of the LocalLink Protocol                         | 248 |  |  |  |

|    | 5.5  | Proces                            | sor Modelling with Different Levels of Abstraction          | 248 |  |  |  |

|    |      | 5.5.1                             | Forms of ISS and Their Variants                             | 249 |  |  |  |

|    |      | 5.5.2                             | Using the C Preprocessor to Adapt Firmware                  | 251 |  |  |  |

|    |      | 5.5.3                             | ESL Cache Modelling and DMI                                 | 253 |  |  |  |

|    | 5.6  | ESL Mo                            | odelling of Power, Performance and Area                     | 254 |  |  |  |

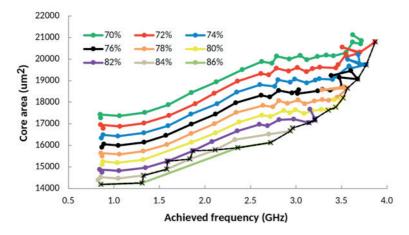

|    |      | 5.6.1                             | Estimating the Operating Frequency and Power with RTL       | 254 |  |  |  |

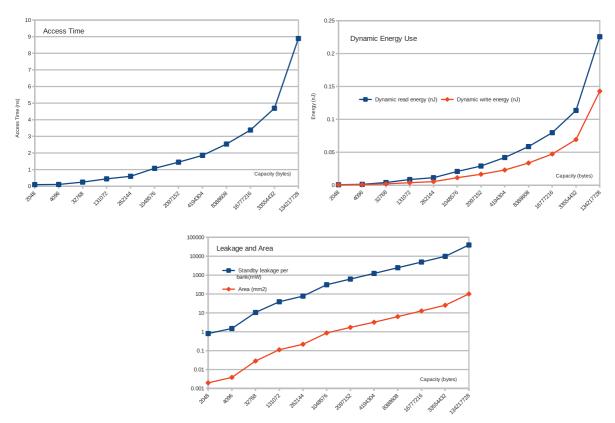

|    |      | 5.6.2                             | Typical Macroscopic Performance Equations: SRAM Example     | 257 |  |  |  |

|    |      | 5.6.3                             | Typical Macroscopic Performance Equations: DRAM Example     | 259 |  |  |  |

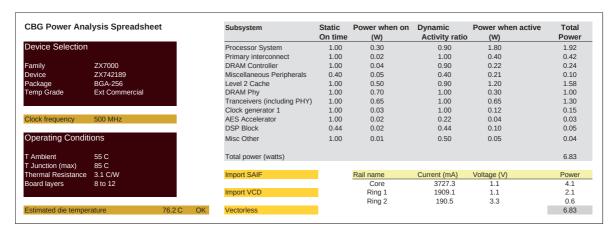

|    |      | 5.6.4                             | Macroscopic Phase and Mode Power Estimation Formula         | 262 |  |  |  |

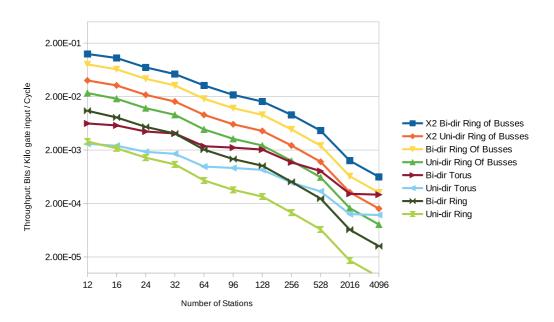

|    |      | 6.6.3    | Illustration 3: NoC Topology Trade-off                                      | 311 |

|----|------|----------|-----------------------------------------------------------------------------|-----|

|    |      | 6.6.4    | Illustration 4: Static and Dynamic Power Trade-off                          | 314 |

|    | 6.7  | Virtual  | Platform Examples                                                           | 315 |

|    |      | 6.7.1    | The Prazor/Zynq Virtual Platform                                            | 315 |

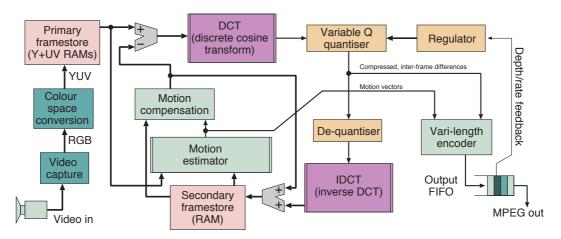

|    |      | 6.7.2    | Co-design Worked Example: MPEG Video Compression                            | 317 |

|    | 6.8  | Design-  | entry Languages                                                             | 320 |

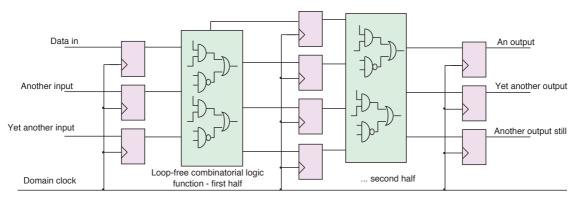

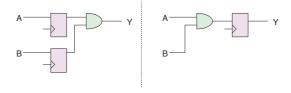

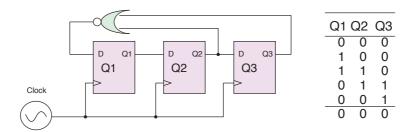

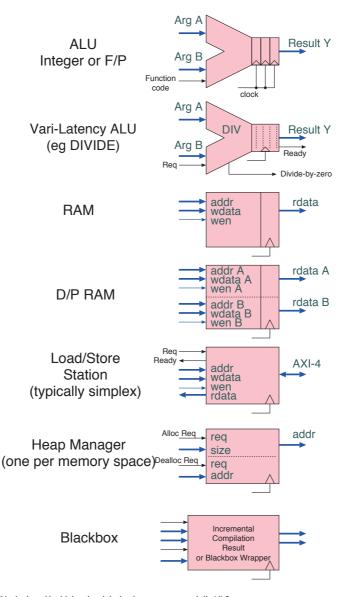

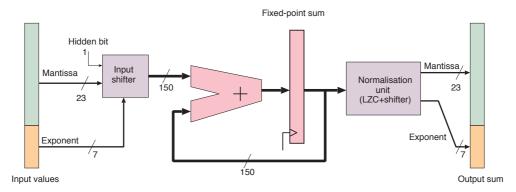

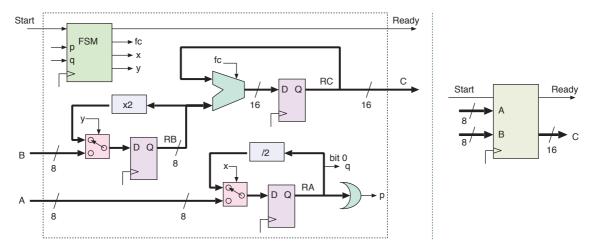

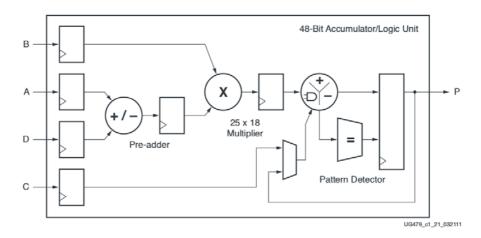

|    |      | 6.8.1    | Functional Units                                                            | 323 |

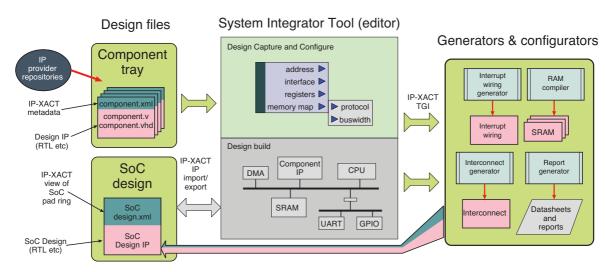

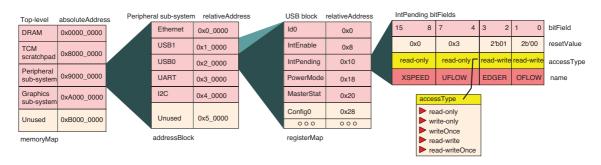

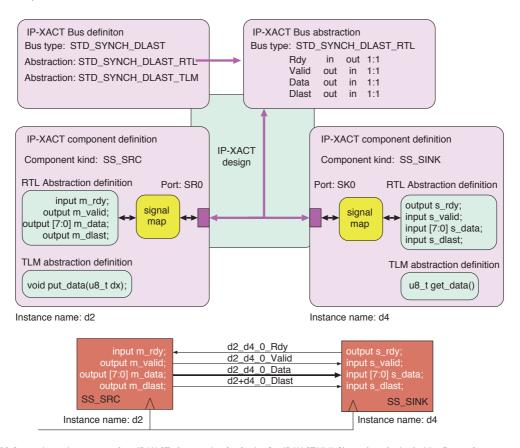

|    |      | 6.8.2    | Accellera IP-XACT                                                           | 326 |

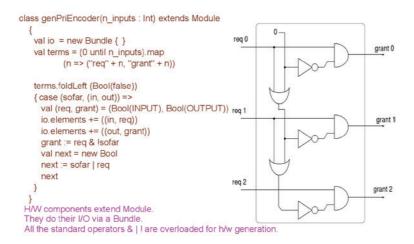

|    |      | 6.8.3    | Hardware Construction Languages                                             | 331 |

|    |      | 6.8.4    | Handel-C                                                                    | 334 |

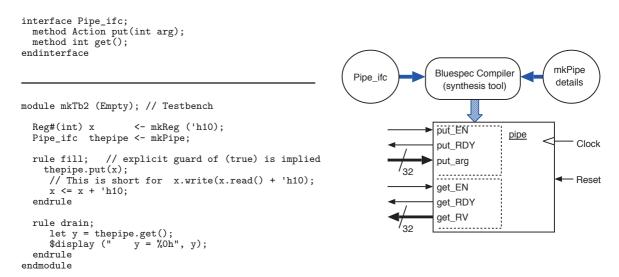

|    |      | 6.8.5    | Bluespec System Verilog                                                     | 335 |

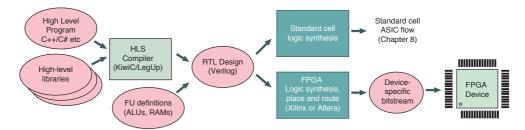

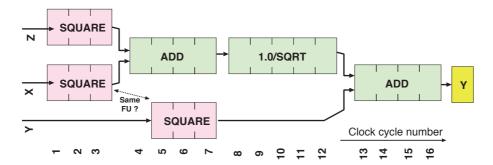

|    | 6.9  | High-le  | vel Synthesis                                                               | 339 |

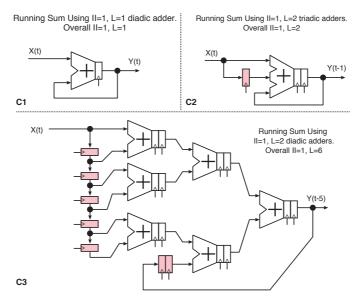

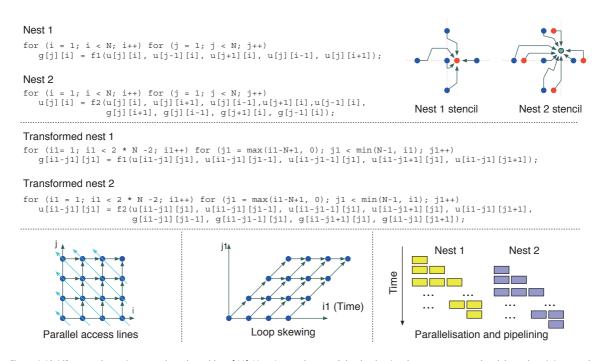

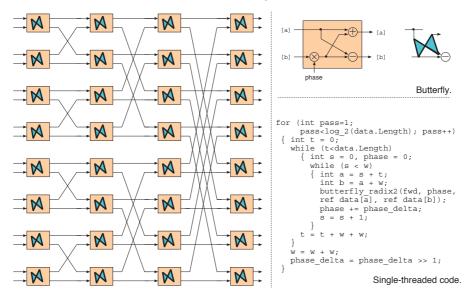

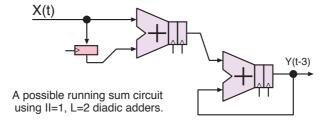

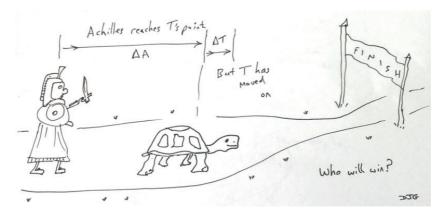

|    |      | 6.9.1    | Discovering Parallelism and Shared Variables in Iterations                  | 347 |

|    | 6.10 | Summa    | ry                                                                          | 356 |

|    |      | 6.10.1   | Exercises                                                                   | 357 |

|    |      |          |                                                                             |     |

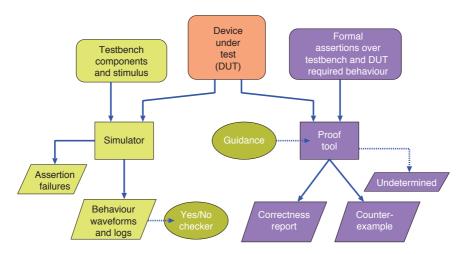

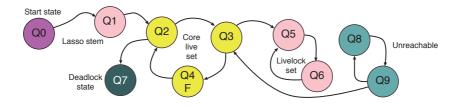

| 7. | Form | al Metho | ods and Assertion-based Design                                              |     |

|    | 7.1  | Formal   | Languages and Tools                                                         | 365 |

|    |      | 7.1.1    | Verification Coverage                                                       | 367 |

|    |      | 7.1.2    | Property Completeness                                                       | 369 |

|    |      | 7.1.3    | When Is a Formal Specification Complete?                                    | 369 |

|    | 7.2  | Assertio | ons                                                                         | 370 |

|    |      | 7.2.1    | Predicate and Property Forms                                                | 373 |

|    |      | 7.2.2    | Assertion-based Design                                                      | 374 |

|    |      | 7.2.3    | Regression Testing                                                          | 375 |

|    | 7.3  | Simulat  | ion with Assertions                                                         | 375 |

|    |      | 7.3.1    | Simulations and Dynamic Validation                                          | 376 |

|    |      | 7.3.2    | Automated Stimulus Generation: Directed and Constrained Random Verification | 376 |

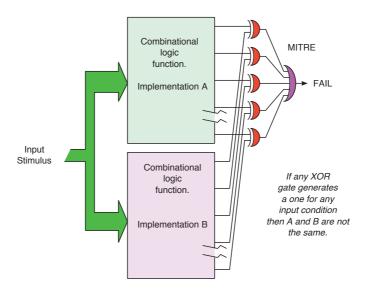

|    |      | 7.3.3    | Simulation versus Formal Checking                                           | 378 |

|    |      |          |                                                                             |     |

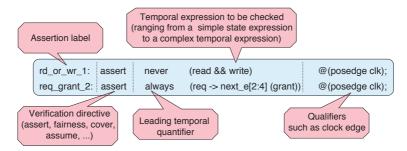

|    | 7.4  | Proper    | ty Specification Language                    | 380 |

|----|------|-----------|----------------------------------------------|-----|

|    |      | 7.4.1     | PSL Four-level Syntax Structure              | 382 |

|    |      | 7.4.2     | Extended Regular Expressions and SERES       | 383 |

|    |      | 7.4.3     | System Verilog Assertions                    | 384 |

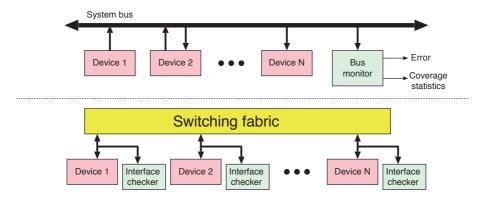

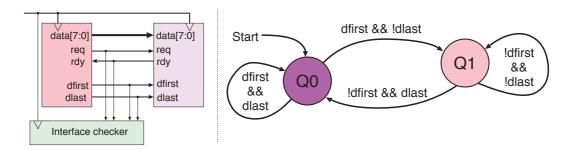

|    | 7.5  | Formal    | Interface Protocol Checkers                  | 385 |

|    | 7.6  | Equiva    | lence Checking                               | 389 |

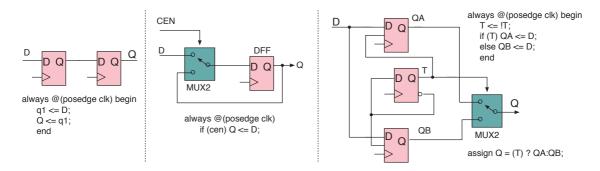

|    |      | 7.6.1     | Boolean Equivalence Checking                 | 389 |

|    |      | 7.6.2     | Sequential Equivalence Checking              | 390 |

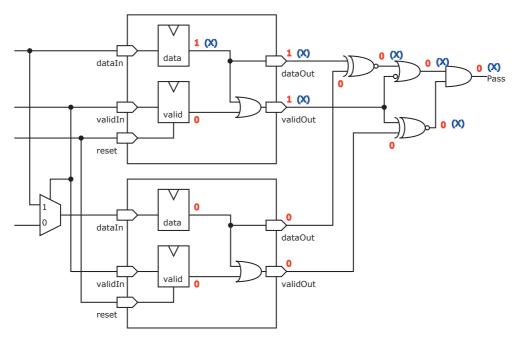

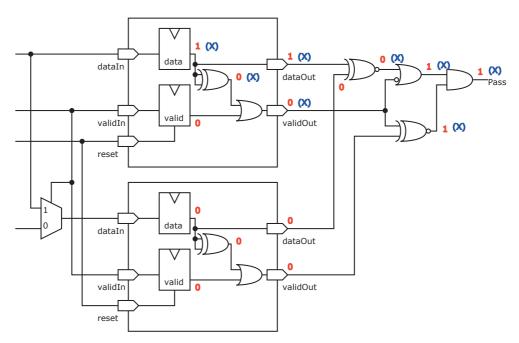

|    |      | 7.6.3     | X-propagation Checking                       | 392 |

|    |      | 7.6.4     | Model Checking the Items in a Data Path      | 396 |

|    | 7.7  | Connec    | ctivity Checking                             | 398 |

|    | 7.8  | Checki    | ing the Security Policy                      | 399 |

|    | 7.9  | Summa     | ary                                          | 399 |

|    |      | 7.9.1     | Exercises                                    | 401 |

| 8. | Fabr | ication a | and Production                               |     |

|    | 8.1  | Evoluti   | ion of Design Closure                        | 405 |

|    |      | 8.1.1     | Physically Aware Design Flows                | 407 |

|    | 8.2  | VLSI G    | eometry                                      | 410 |

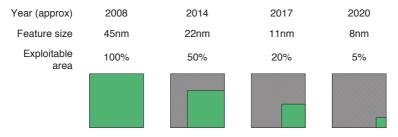

|    |      | 8.2.1     | VLSI Evolution                               | 412 |

|    |      | 8.2.2     | Typical and Future Values                    | 415 |

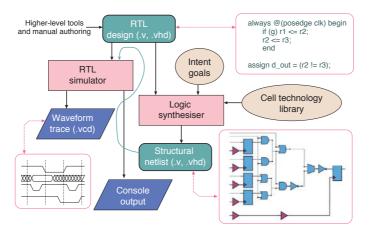

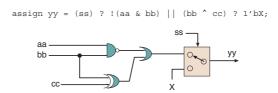

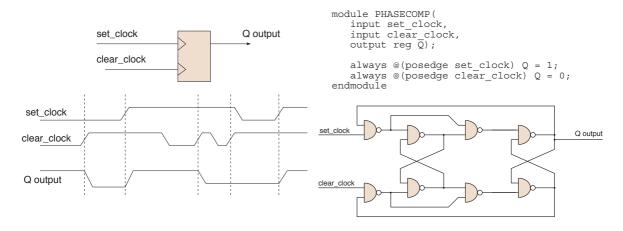

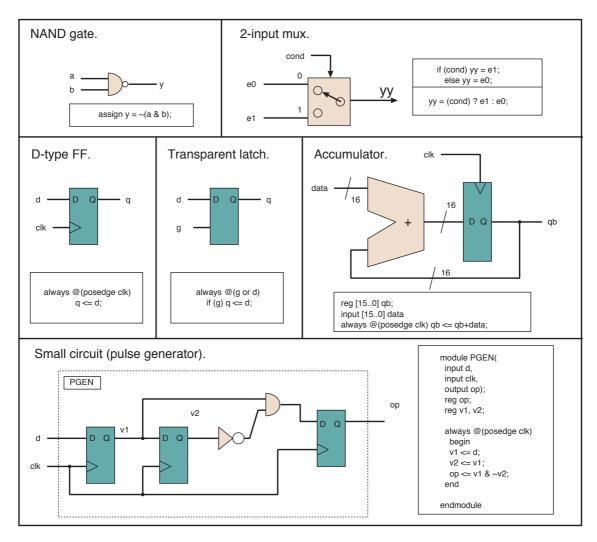

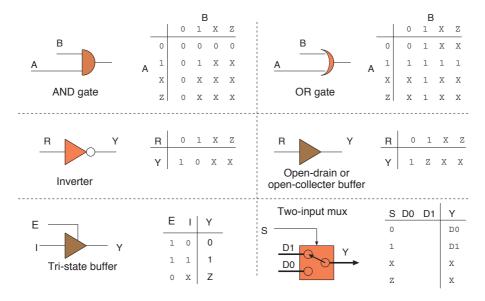

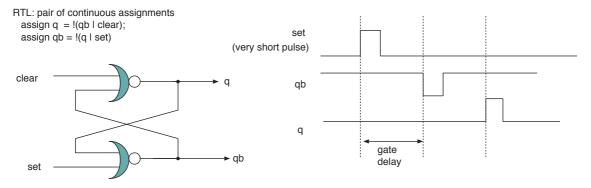

|    | 8.3  | Registe   | er Transfer Languages                        | 418 |

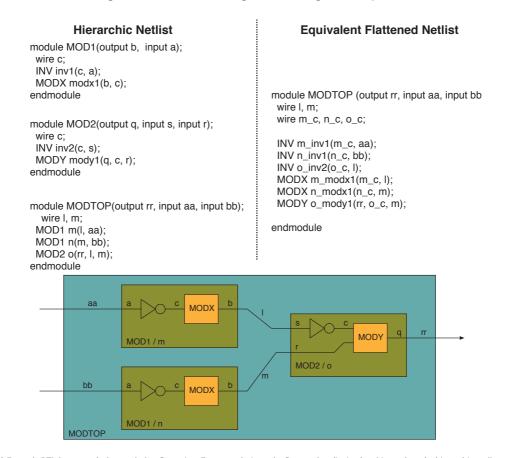

|    |      | 8.3.1     | RTL Structural Elaboration                   | 420 |

|    |      | 8.3.2     | Unsynthesisable RTL                          | 427 |

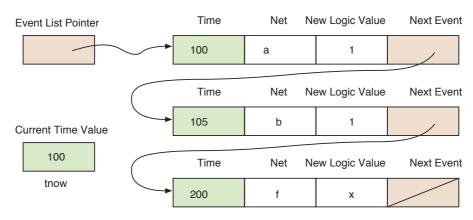

|    |      | 8.3.3     | RTL Simulation Algorithms                    | 429 |

|    |      | 8.3.4     | Event-driven Simulation                      | 431 |

|    |      | 8.3.5     | Inertial and Transport Delays                | 431 |

|    |      | 8.3.6     | Compute/Commit Modelling and the Delta Cycle | 432 |

|    |      | 8.3.7     | Mixed Analogue and Digital Simulation        | 433 |

|    |      |           |                                              |     |

|     | 8.3.8   | Logic Synthesis                         | 439 |

|-----|---------|-----------------------------------------|-----|

|     | 8.3.9   | Arrays and RAM Inference in RTL         | 442 |

|     | 8.3.10  | Memory Macrocell Compiler               | 443 |

|     | 8.3.11  | Conventional RTL Compared with Software | 444 |

|     | 8.3.12  | Synthesis Intent and Goals              | 445 |

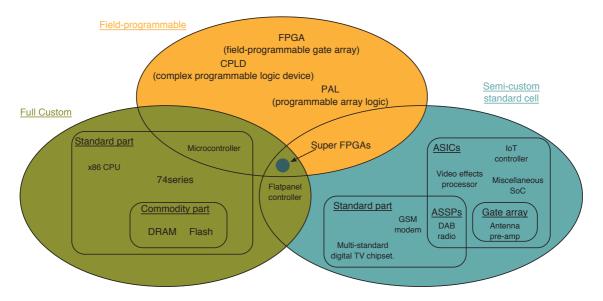

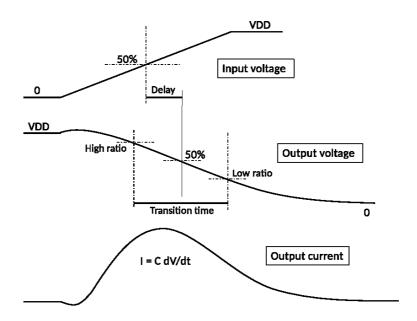

| 8.4 | Chip Ty | pes and Classifications                 | 448 |

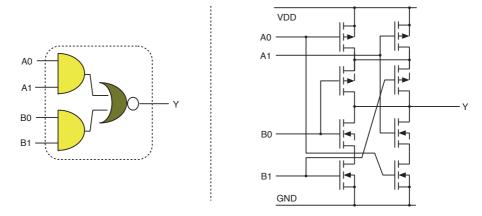

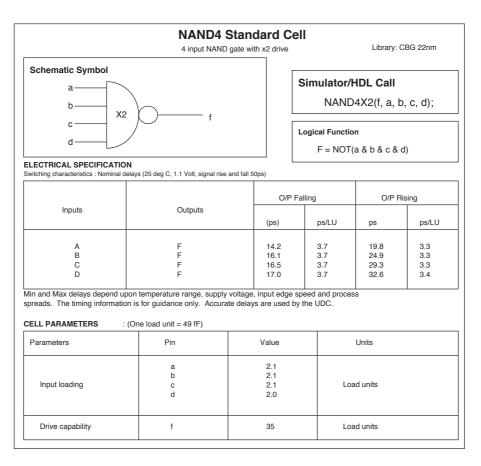

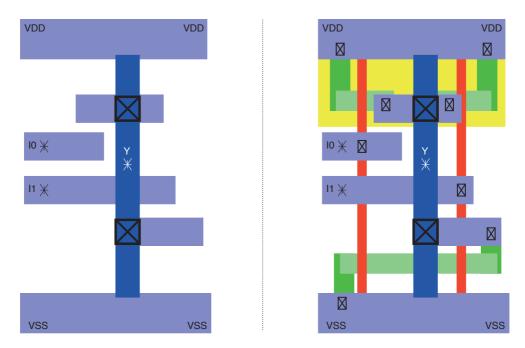

|     | 8.4.1   | Semi-custom (Cell-based) Design         | 452 |

|     | 8.4.2   | Standard Cell Data                      | 454 |

|     | 8.4.3   | SPICE Characterisation                  | 455 |

|     | 8.4.4   | PVT Variations                          | 456 |

|     | 8.4.5   | Electromigration                        | 456 |

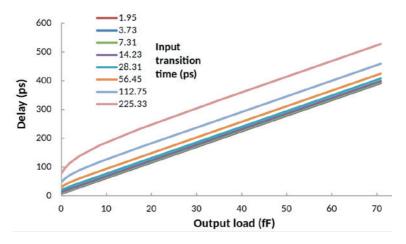

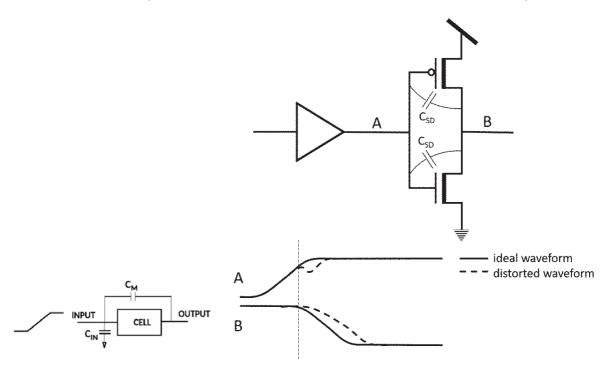

|     | 8.4.6   | Waveform-based Cell Characterisation    | 458 |

|     | 8.4.7   | Noise Characterisation                  | 460 |

| 8.5 | Gate A  | rrays                                   | 461 |

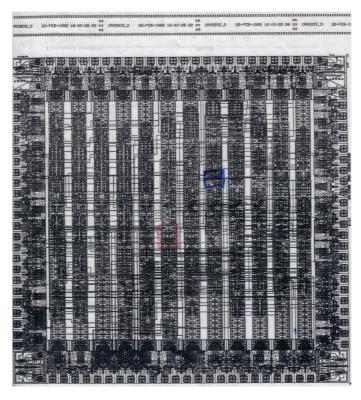

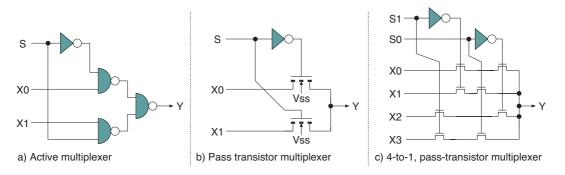

|     | 8.5.1   | Pass-transistor Multiplexers            | 462 |

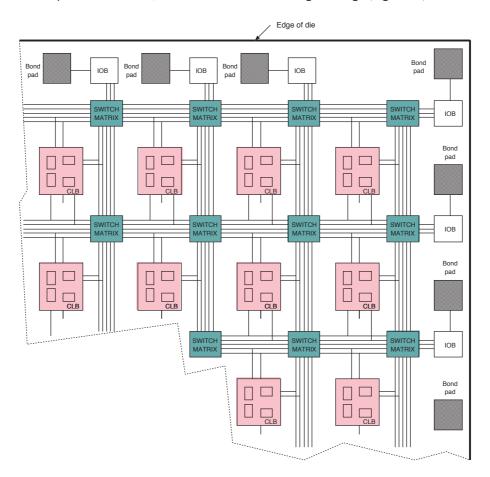

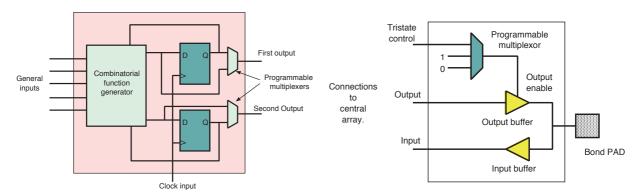

|     | 8.5.2   | Field-programmable Gate Arrays          | 464 |

|     | 8.5.3   | Structured ASIC                         | 467 |

|     | 8.5.4   | FPGA SoC Emulators                      | 467 |

| 8.6 | Floor a | nd Power Planning                       | 468 |

|     | 8.6.1   | Power Planning                          | 468 |

| 8.7 | Flow St | teps                                    | 470 |

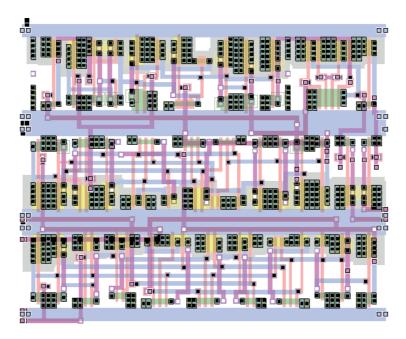

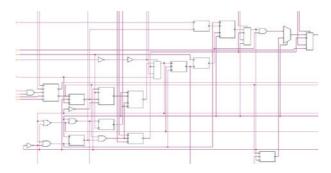

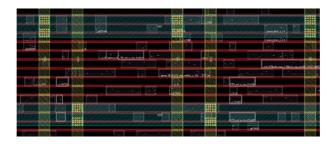

|     | 8.7.1   | Placement                               | 470 |

|     | 8.7.2   | Clock Tree Insertion                    | 473 |

|     | 8.7.3   | Routing                                 | 473 |

|     | 8.7.4   | Timing and Power Verification           | 474 |

|     | 8.7.5   | Post-route Optimisation                 | 475 |

|     | 8.7.6   | Layout versus Schematic Check           | 475 |

|     | 8.7.7   | Sign-off and Tapeout                    | 475 |

| 8.8  | Producti  | ion Testing                                                          | 476 |  |  |  |

|------|-----------|----------------------------------------------------------------------|-----|--|--|--|

|      | 8.8.1     | Universal Verification Methodology and Open Verification Methodology | 477 |  |  |  |

|      | 8.8.2     | Test Program Generation                                              | 478 |  |  |  |

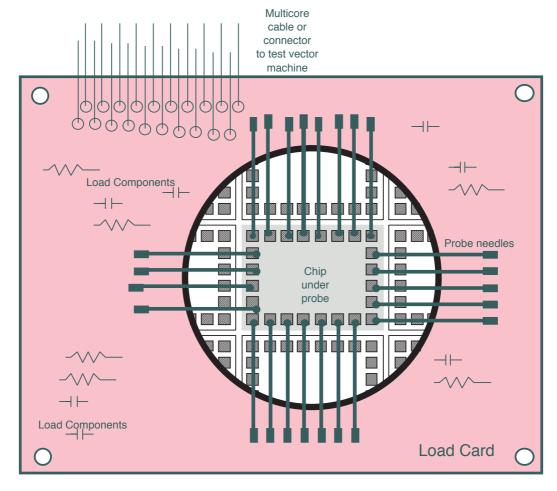

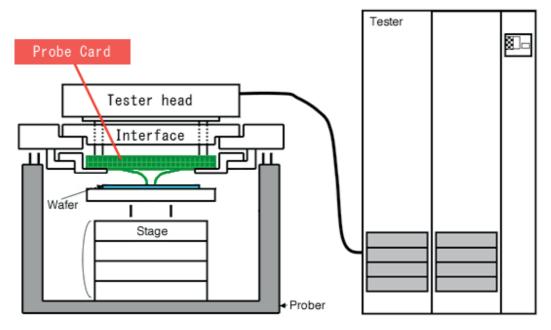

|      | 8.8.3     | Wafer Probe Testing                                                  | 480 |  |  |  |

|      | 8.8.4     | Packaged Device Testing                                              | 482 |  |  |  |

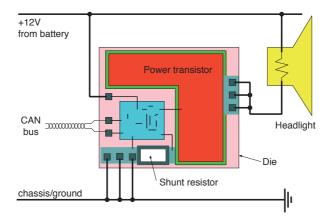

| 8.9  | Device P  | Device Packaging and MCMs                                            |     |  |  |  |

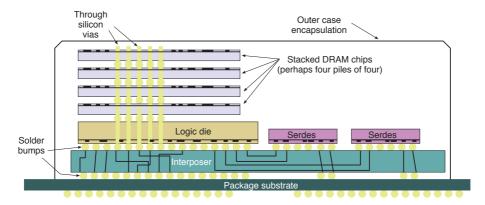

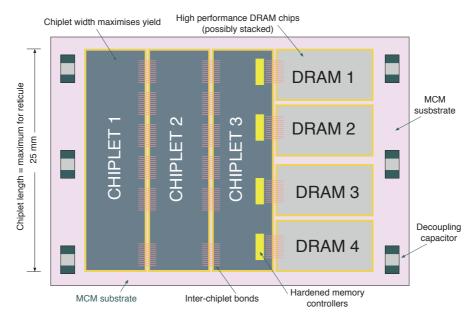

|      | 8.9.1     | MCMs and Die-stacking                                                | 484 |  |  |  |

| 8.10 | Enginee   | ring Change Orders                                                   | 485 |  |  |  |

| 8.11 | ASIC Co   | ests: Recurring and Non-recurring Expenses                           | 487 |  |  |  |

|      | 8.11.1    | Chip Cost versus Area                                                | 487 |  |  |  |

| 8.12 | Static Ti | iming Analysis and Timing Sign-off                                   | 488 |  |  |  |

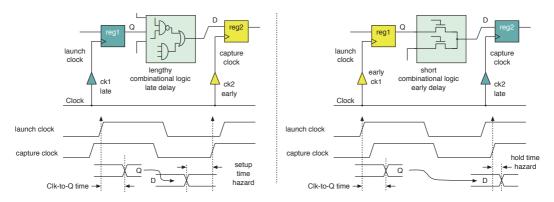

|      | 8.12.1    | STA Types: Maximum and Minimum                                       | 489 |  |  |  |

|      | 8.12.2    | Maximum Timing Analysis                                              | 489 |  |  |  |

|      | 8.12.3    | Minimum Timing Analysis                                              | 491 |  |  |  |

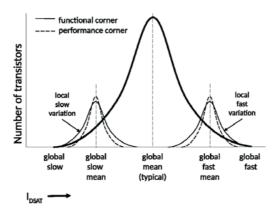

|      | 8.12.4    | Process Corners                                                      | 492 |  |  |  |

|      | 8.12.5    | Early and Late Arrivals                                              | 494 |  |  |  |

|      | 8.12.6    | Timing Models: Liberty                                               | 496 |  |  |  |

|      | 8.12.7    | Multi-mode Multi-corner Analysis                                     | 499 |  |  |  |

|      | 8.12.8    | Signal Integrity                                                     | 500 |  |  |  |

|      | 8.12.9    | Coupling Capacitance                                                 | 500 |  |  |  |

|      | 8.12.10   | Noise Analysis                                                       | 501 |  |  |  |

|      | 8.12.11   | Transition Time Limits                                               | 501 |  |  |  |

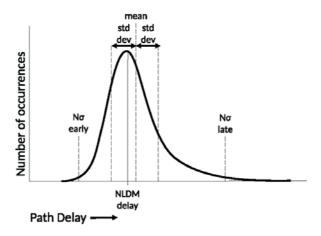

|      | 8.12.12   | On-chip Variation                                                    | 502 |  |  |  |

|      | 8.12.13   | Net Delay Variation                                                  | 504 |  |  |  |

|      | 8.12.14   | Voltage Variation                                                    | 505 |  |  |  |

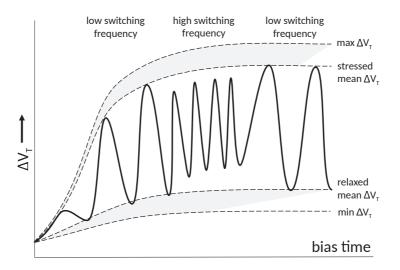

|      | 8.12.15   | Advanced Topics in STA                                               | 505 |  |  |  |

|      | 8.12.16   | Timing Closure                                                       | 506 |  |  |  |

| 8.13 | Summar    | ry                                                                   | 507 |  |  |  |

|      | 8.13.1    | Exercises                                                            | 508 |  |  |  |

| Putt  | tting Everything Together        |     |  |

|-------|----------------------------------|-----|--|

| 9.1   | Firmware                         | 512 |  |

|       | 9.1.1 Secure Bootstrapping       | 513 |  |

| 9.2   | Powering up                      | 514 |  |

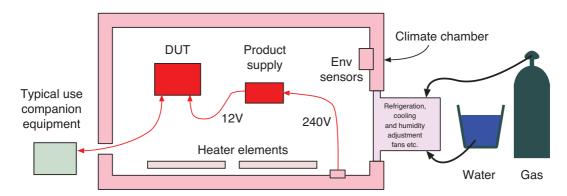

|       | 9.2.1 Engineering Sample Testing | 514 |  |

| 9.3   | Success or Failure?              | 517 |  |

| Gloss | sary of Abbreviations            | 521 |  |

| Index | ×                                | 551 |  |

#### **Preface**

Silicon technology has seen relentless advances in the past 50 years, driven by constant innovation and miniaturisation. As a result, more and more functionality has been placed into a single chip. Today, entire systems, including processors, memory, sensors and analogue circuitry, are integrated into one single chip (hence, a system-on-chip or SoC), delivering increased performance despite tight area, power and energy budgets. The aim of this textbook is to expose aspiring and practising SoC designers to the fundamentals and latest developments in SoC design and technologies. The processors within a SoC run a huge body of software. Much of this code is portable over many platforms, but low-level components, such as device drivers, are hardware-dependent and may be CPU-intensive. Power use can be reduced using custom accelerator hardware. Although this book emphasises the hardware design elements, it also addresses *co-design*, in which the hardware and software are designed hand in hand. It is assumed that the reader already understands the basics of processor architecture, computer technology, and software and hardware design.

#### Is This Book Suitable For You?

We assume that you have some experience with hardware design using an RTL such as Verilog or VHDL, and that you understand assembly language programming and basic principles of operating systems. In other words, you have completed the first two years of a degree in Computer Science or Electronic Engineering.

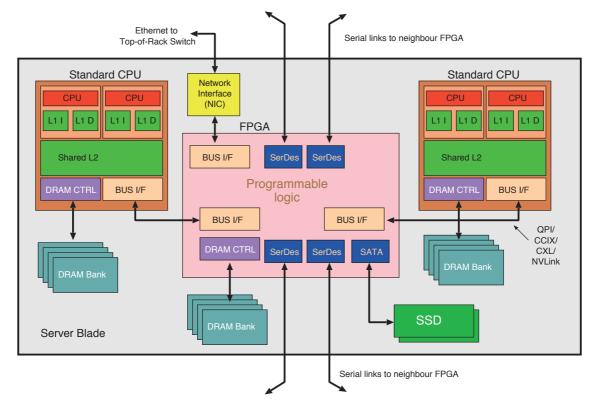

Many of the principles taught in this book are relevant for all forms of system architect, including those who are designing cloud-scale applications, custom accelerators or IoT devices in general, or those making FPGA designs. But the details of design verification in Chapter 8 are likely to be just of interest to those designing semi-custom silicon using standard cells.

A Git repository of **online additional material** is available at http://bitbucket.org/djg11/modern-soc-design-djg

This contains data used for generating tables and graphs in the book, as well as further source code, lab materials, examples and answers to selected exercises.

The repo contains a SystemC model of the Zynq super FPGA device family, coded in blocking TLM style. It is sufficient to run an Arm A9 Linux kernel using an identical boot image as the real silicon.

#### **Book Structure**

This book contains nine chapters, each devoted to a different aspect of SoC design.

Chapter 1 reviews basic computer architecture, defining terms that are used in later chapters. Readers are expected to be largely familiar with most of this material, although the transactional-level modelling (TLM) view of the hardware is likely to be new. A SoC is an assembly of intellectual property (IP) blocks.

Chapter 2 describes many of the standard IP blocks that make up a typical SoC, including processors, memories, input/output devices and interrupts.

Chapter 3 considers the interconnect between the IP blocks, covering the evolution of processor busses and networks-on-chip (NoCs).

Chapter 4 teaches basic principles of system architecture, including dimensioning of busses and queuing theory and arbitration policies. It also discusses debug support.

Chapter 5 presents Electronic System Level (ESL) modelling, where a simulation model for a whole SoC, also known as a virtual platform, is put together. The ESL model is sufficient to test and develop software, as well as to perform architectural exploration, where the throughput, energy use and silicon area of a proposed system implementation can be examined at a high level.

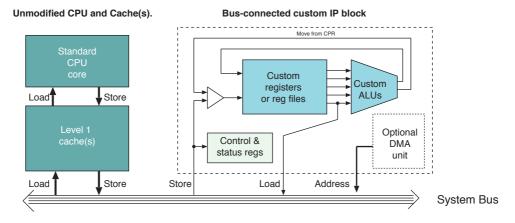

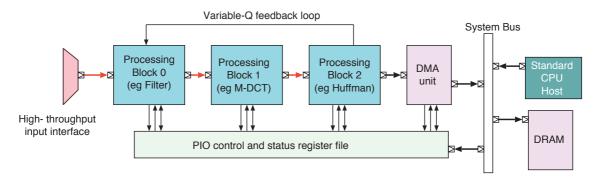

Chapter 6 presents further architectural exploration considerations, including the design of custom accelerators for a specific application. The languages Bluespec and Chisel are described as alternatives to RTL for design entry and the basic principles of high-level synthesis (HLS) are covered.

Chapter 7 is a primer for formal verification of SoCs, comparing the usefulness of formal compared with simulation for bug hunting and right-first-time solutions. A number of useful formal tricks are covered.

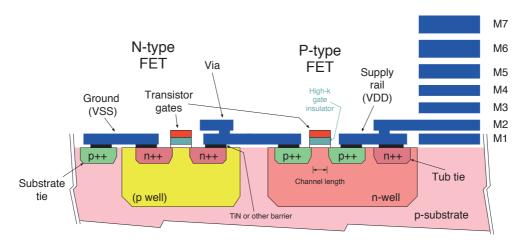

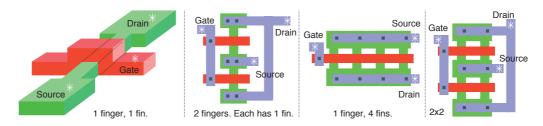

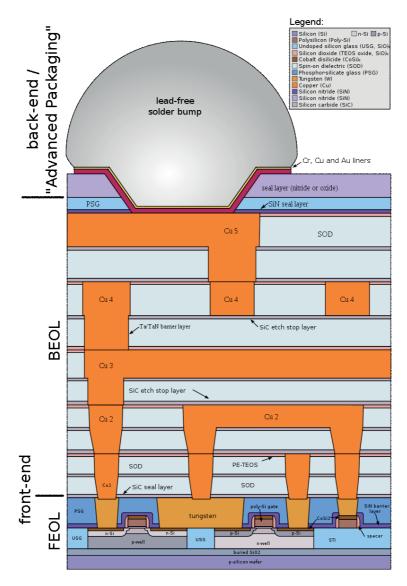

Chapter 8 presents semi-custom fabrication flows for making the physical silicon and covers advanced verification and variability mitigation techniques for today's deep sub-micron devices using FinFETs.

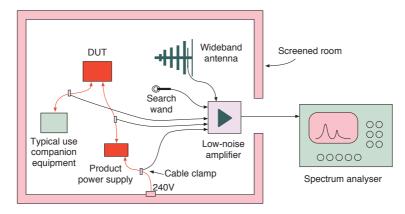

Chapter 9 covers what to do when the first SoC samples arrive back from the wafer processing plant, including booting an operating system and checking environmental compatibility (operating temperature and unwanted radio emissions).

### **Acknowledgements**

I am very grateful to Professor Sir Andy Hopper, who was my PhD supervisor, who has been a constant source of inspiration and direction, and who has often been my boss both in industry and at the Computer Laboratory. He introduced me to the field of chip design. I am also very grateful to the late M. G. Scroggie, the principal author of 'Foundations of Wireless', which was a book I read and re-read all through my childhood. I can only hope some people find this current book as valuable as I found his. Certainly I have tried to mix breadth and depth in the same accessible way that he managed. I would like to thank those working in the Computer Laboratory who helped with this book, including David Chisnall, Robert Mullins, Omer Sella and Milos Puzovic. I would also like to thank my wife, Aldyth, for putting up with me for this last year. I've often read such comments in the acknowledgement sections of other books, but now I understand what causes it.

Most importantly, I'd like to thank the many Arm staff who have helped with this book, either by contributing text to large chunks of it, or with additional information and suggestions:

Khaled Benkrid, who made this book possible.

Liz Warman, who kept me on track and assisted me with the process.

Shuojin Hang and Francisca Tan who helped create the scope and reviewed early drafts.

This book would not have been possible without the collaboration of the following Arm engineers who have co-written, reviewed and commented on the book:

- Chapter 2: Processors, Memory and IP Blocks Rahul Mathur, Staff Engineer

- Chapter 3: SoC Interconnects

Anup Gangwar, Distinguished Engineer

Antony Harris, Senior Principal AMBA Architect

- Chapter 6: Architectural Design Exploration

Edwin Dankert, Director, Technology Management

- Chapter 7: Formal Methods and Assertion-Based Design Daryl Stewart, Distinguished Engineer

- Chapter 8: Fabrication and Production Jim Dodrill, Fellow

Christophe Lopez, Senior Principal Engineer

Aurelien Merour, Principal Engineer

Jean-Luc Pelloie, Fellow

### **Author Biography**

**Dr. David J. Greaves**, PhD CEng. is Senior Lecturer in Computing Science at the University of Cambridge, UK and a Fellow of Corpus Christi College. Born in London, he grew up in a house full of engineering textbooks, circuit diagrams and pieces of telecommunications equipment. His grandfather had built his own television set as soon as television broadcasts started. His father worked at EMI and IBM, developing modems and computer interfaces. With the shift of head office of IBM UK to Portsmouth, the family moved to Romsey in Hampshire.

Plessey Roke Manor was also situated in Romsey, along with IBM's UK research laboratories at Hursley Park. These were, and remain, world-leading research centres in the field of radio communications and computing. The young David J. Greaves was a regular visitor and intern at both sites, and by the age of 17 had designed and built his first computer. The chips had been mostly removed from old circuit boards using a blow lamp. The software, including the disk operating system and a Pascal compiler, had all been written from scratch.

During his A-level studies, Greaves designed a local area network for Commodore PET computers. The design was published in Wireless World magazine and commercially replicated.

As an undergraduate at St John's College Cambridge, he offered consultancy services to various small electronics companies in the field of professional audio, developing MIDI interfaces and low-noise pre-amplifiers. His final-year degree project was a fully digital keyboard instrument that was serialised in Wireless World and copied by many enthusiasts worldwide. A main interest became the design and implementation of compilers, as encouraged by Dr. Martin Richards of St Johns, who had developed the BCPL language, the direct precursor of C.

Greaves designed his first silicon chips during his PhD studies, which were in the field of metropolitan area networks. He designed fibre optic transceivers that sent the first mono-mode signals over the newly installed fibres that criss-crossed Cambridge. In collaboration with Acorn Computer, in 1995 Greaves was the chief network architect for the Cambridge ITV trial, which put ATM switches in the kerbside cabinets belonging to Cambridge Cable Ltd and delivered video on demand to 50 or so homes. It was 20 years later that the last movie rental shop in Cambridge closed.

Also in 1995, he implemented CSYN, one of the first Verilog compilers for synthesising hardware specifically for field programmable gate arrays. This compiler was distributed widely among local companies on the Cambridge Science Park and also used for undergraduate teaching. It was licensed to a multinational to bundle with its own family of FPGAs.

Greaves had visited Arm when it first spun out of Acorn and consisted of six engineers in a barn. At the university, Greaves used a donation of Arm circuit boards for a new practical course in which the

students wrote assembly language and Verilog to learn about low-level hardware and software interfacing. These courses still run today and the lecture notes have evolved into this textbook.

Greaves has been on the board or technical advisory board of at least ten start-up companies. He has supervised or examined more than 60 PhD students. He holds at least five international patents in the field of communications and electronics. His company Tenison EDA was, before acquisition, directly providing tools to all major chip makers. His current research interests remain in the field of compilation tools for design automation and scientific acceleration.

## **List of Figures**

| Figure 1.1  | fragments (right)                                                                                                   | 3  |

|-------------|---------------------------------------------------------------------------------------------------------------------|----|

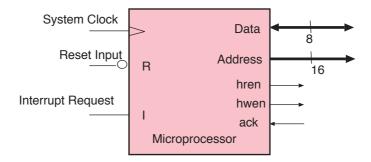

| Figure 1.2  | Schematic symbol and external connections for a tri-state version of a simple microprocessor                        | 4  |

| Figure 1.3  | A simple A16D8 microcomputer structure                                                                              | 5  |

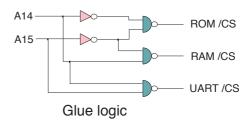

| Figure 1.4  | Connections to memory                                                                                               | 6  |

| Figure 1.5  | MSOC1 reference bus protocol, with read and write examples                                                          | 7  |

| Figure 1.6  | Structure of a typical microcontroller, a single-chip microcomputer                                                 | 9  |

| Figure 1.7  | Hitachi HD614080 microcontroller chip from 1980                                                                     | 9  |

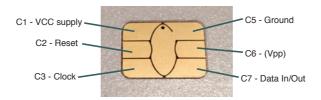

| Figure 1.8  | Contact plate for a smart card                                                                                      | 10 |

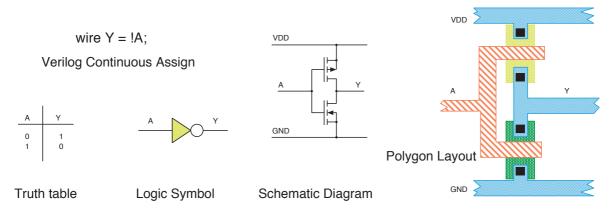

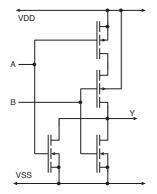

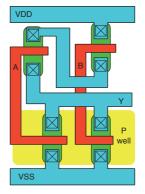

| Figure 1.9  | An invertor viewed at various levels of abstraction                                                                 | 11 |

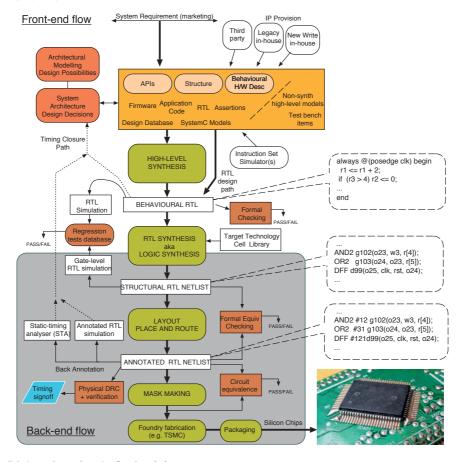

| Figure 1.10 | Front-end flow in SoC design                                                                                        | 12 |

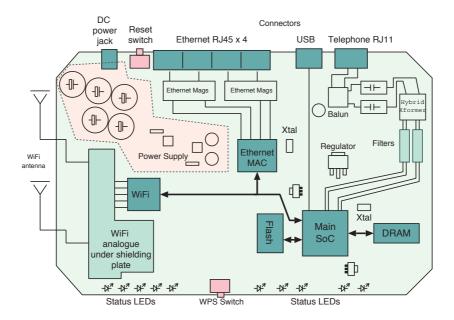

| Figure 1.11 | Main PCB of an ADSL home modem                                                                                      | 13 |

| Figure 1.12 | Main PCB structure of an ADSL home modem                                                                            | 13 |

| Figure 1.13 | Overall design and manufacturing flow for a SoC                                                                     | 18 |

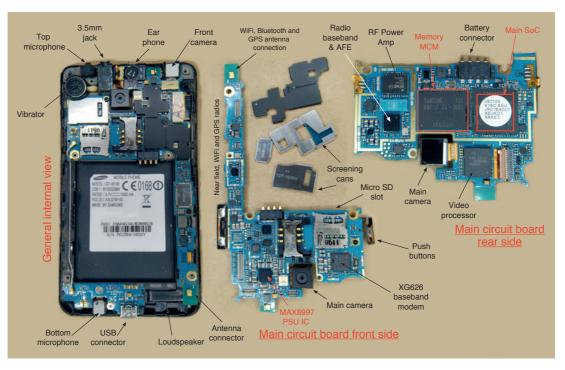

| Figure 1.14 | General internal view of a mobile phone (left) and views of both sides of the main circuit board (centre and right) | 20 |

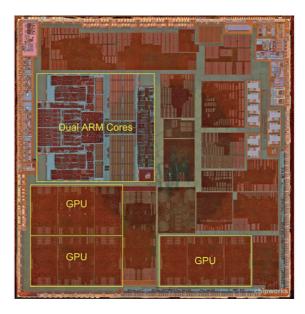

| Figure 1.15 | An Apple SoC with two Arm and three GPU cores                                                                       | 22 |

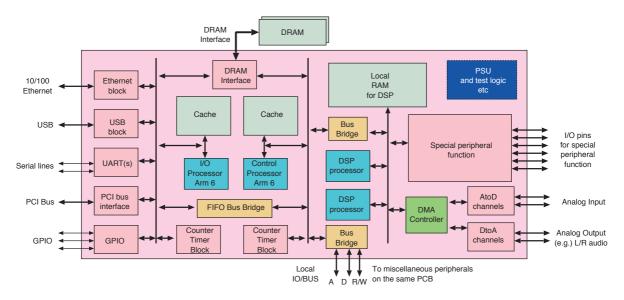

| Figure 1.16 | A platform chip example: the Virata Helium 210, as used in many ADSL modems                                         | 23 |

| Figure 1.17 | Helium chip as part of a home gateway ADSL modem (partially masked by the 802.11 module)                            | 23 |

| Figure 1.18 | Another platform chip intended for use in thin-client display devices, such as a tablet                             | 24 |

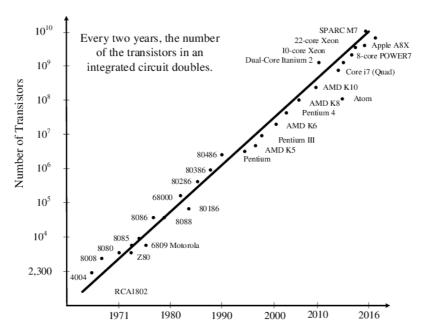

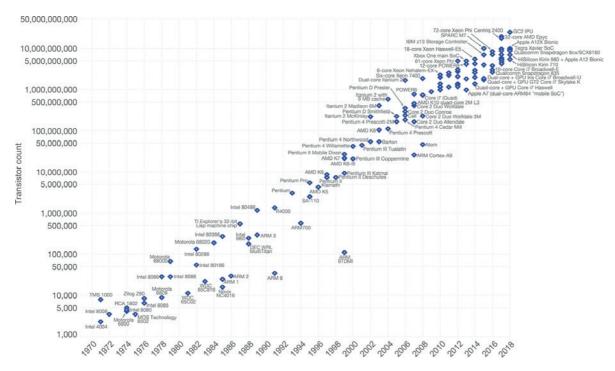

| Figure 1.19 | Moore's law (Section 8.2)                                                                                           | 25 |

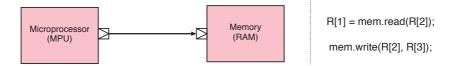

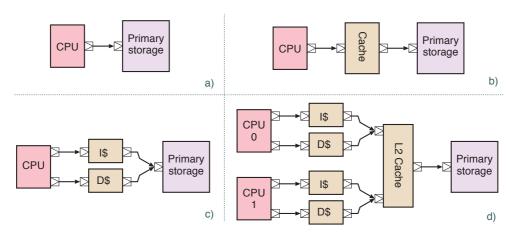

| Figure 2.1  | TLM connection diagrams for CPU and memory configurations                                                           | 28 |

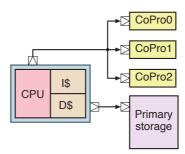

| Figure 2.2  | TLM diagrams for a CPU core with integrated first-level caches and external coprocessor connections                 | 29 |

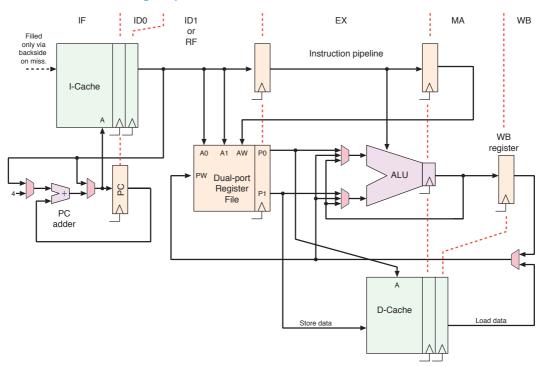

| Figure 2.3  | Main data paths in a generic five-stage RISC microarchitecture, excluding the back sides of the cache and MMU       | 32 |

| Figure 2.4  | Key components of a super-scalar CPU core, excluding the back sides of the cache and $\ensuremath{MMU}$             | 34 |

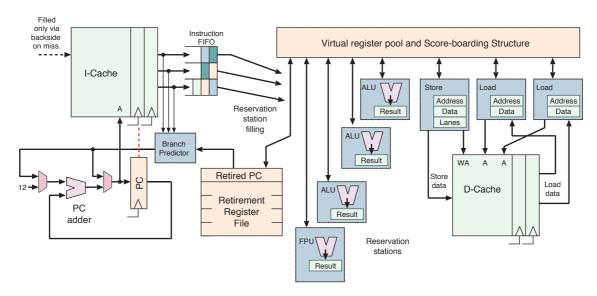

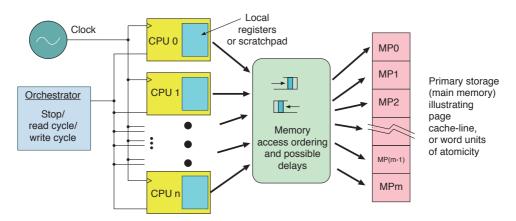

| Figure 2.5  | TLM connection diagrams for a CPU and memory management unit (MMU): (a) naive view and (b) one possible cache arrangement                                         | 36 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

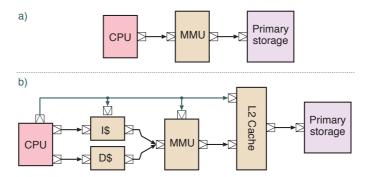

| Figure 2.6  | A generalised PRAM model of computing                                                                                                                             | 38 |

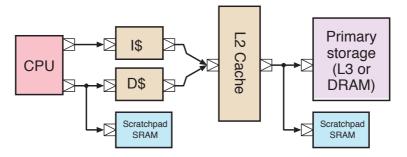

| Figure 2.7  | Two possible configurations for scratchpad memory                                                                                                                 | 39 |

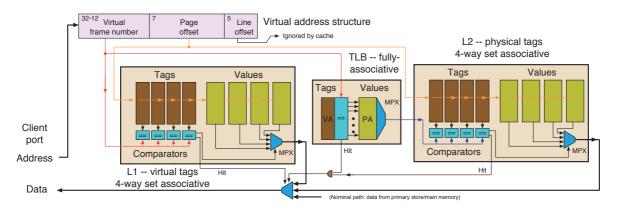

| Figure 2.8  | Typical arrangement of virtual and physical mapping with L1, TLB and L2                                                                                           | 42 |

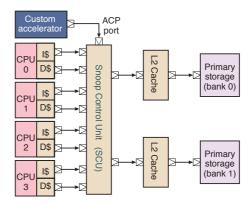

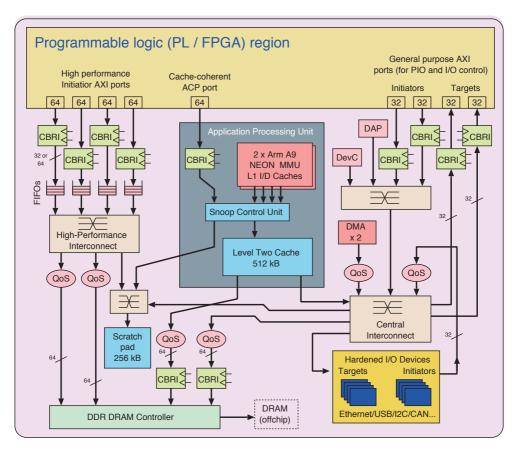

| Figure 2.9  | An example system using a snoop control IP block from Arm (Cortex A9 family)                                                                                      | 45 |

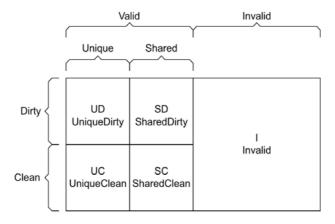

| Figure 2.10 | MOESI-like state diagram used in the Arm ACE and CHI protocols                                                                                                    | 45 |

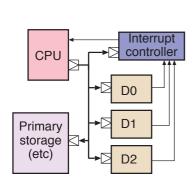

| Figure 2.11 | Three I/O blocks connected to a CPU, memory and an interrupt controller                                                                                           | 46 |

| Figure 2.12 | Three I/O blocks with flexible interrupt distribution in a multi-core system                                                                                      | 46 |

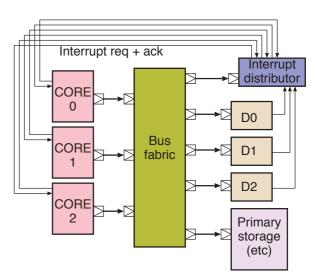

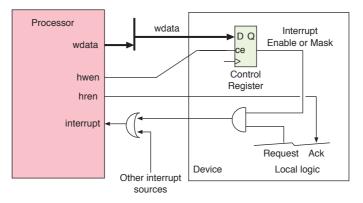

| Figure 2.13 | Interrupt generation: general structure within a device and at system level                                                                                       | 47 |

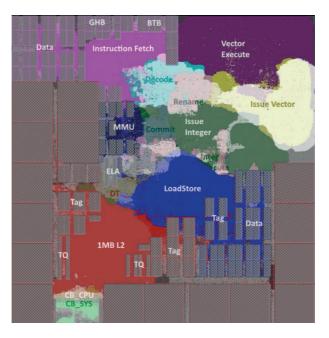

| Figure 2.14 | Floorplan visualisation of a 3D implementation of the Arm Neoverse N1 design using two chips, vertically stacked                                                  | 49 |

| Figure 2.15 | Low-aspect-ratio RAM array showing the shared peripheral circuitry, which includes the word-line decoder, sense amplifiers, tri-state buffers and I/O multiplexer | 50 |

| Figure 2.16 | Mask-programmed NMOS ROM structure with a capacity of $2^N$ locations, each holding an M-bit word                                                                 | 51 |

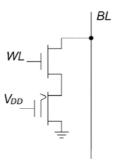

| Figure 2.17 | Transistor-level view of a standard six-transistor (6T) SRAM cell                                                                                                 | 52 |

| Figure 2.18 | SSRAM with a single port, showing the logic symbol (left) and internal RTL model (right)                                                                          | 54 |

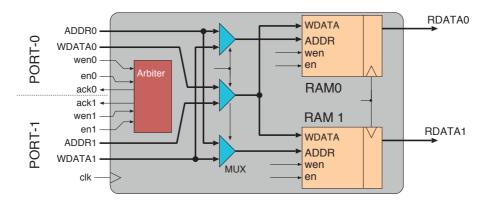

| Figure 2.19 | 8T SRAM cell with true dual-porting                                                                                                                               | 54 |

| Figure 2.20 | Dual-ported SSRAM logic symbol                                                                                                                                    | 54 |

| Figure 2.21 | Micrograph of a simple DRAM chip circa 1994                                                                                                                       | 55 |

| Figure 2.22 | Left: pinout for a typical asynchronous. Right: basic internal structure schematic                                                                                | 55 |

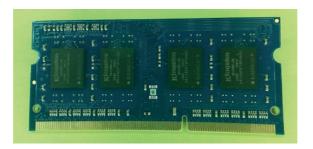

| Figure 2.23 | 4-Gbyte DRAM dual in-line memory module (DIMM) for a laptop computer                                                                                              | 57 |

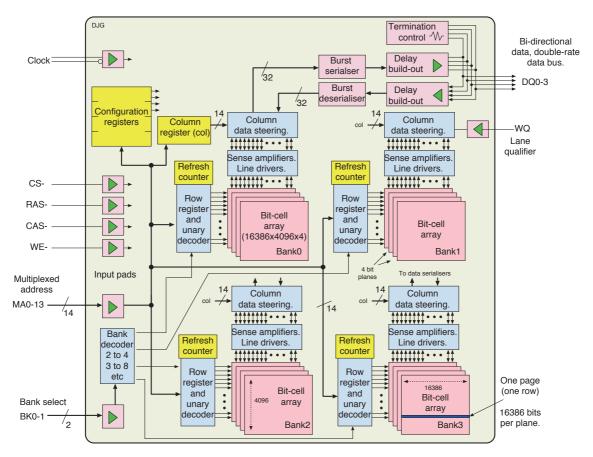

| Figure 2.24 | Internal block diagram of a 4-bit-wide DRAM device                                                                                                                | 58 |

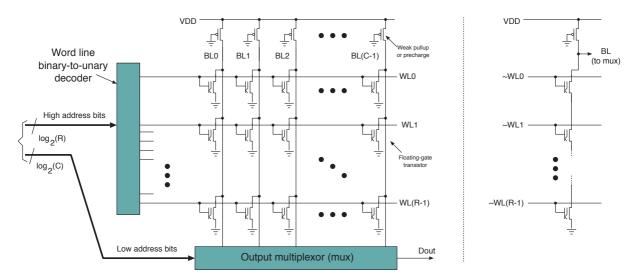

| Figure 2.25 | NOR ROM block diagram (left) with capacity $2^{(R+C)}$ bits and alternative NAND ROM array detail (right)                                                         | 60 |

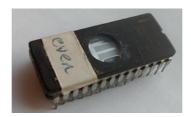

| Figure 2.26 | EPROM device from the 1980s                                                                                                                                       | 61 |

| Figure 2.27 | Schematic of a possible bit cell for EPROM and EEPROM                                                                                                             | 62 |

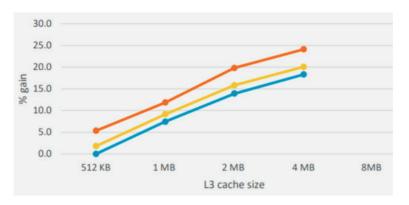

| Figure 2.28 | Typical increase in benchmark performance in response to L3 cache size enlargement for L2=64 KB (blue), L2 = $128$ KB (yellow) and L2 = $256$ KB (red)            | 64 |

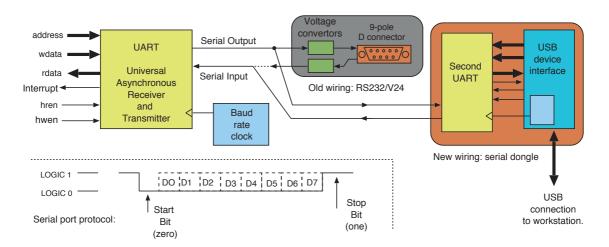

| Figure 2.29 | Typical I/O ports. Shown are two serial ports, one parallel port, one Ethernet port, two USB ports and three audio ports                                  | 65  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.30 | Two typical configurations for a serial port using a UART                                                                                                 | 65  |

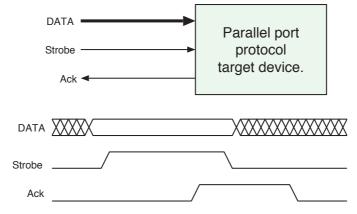

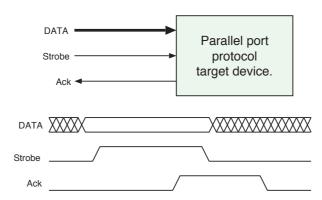

| Figure 2.31 | Timing diagram for an asynchronous four-phase handshake                                                                                                   | 68  |

| Figure 2.32 | Schematic and RTL implementation of 32 GPIO bits connected to an MSOC1 bus                                                                                | 70  |

| Figure 2.33 | Schematic symbol for a counter/timer block and internal RTL for one timer function                                                                        | 71  |

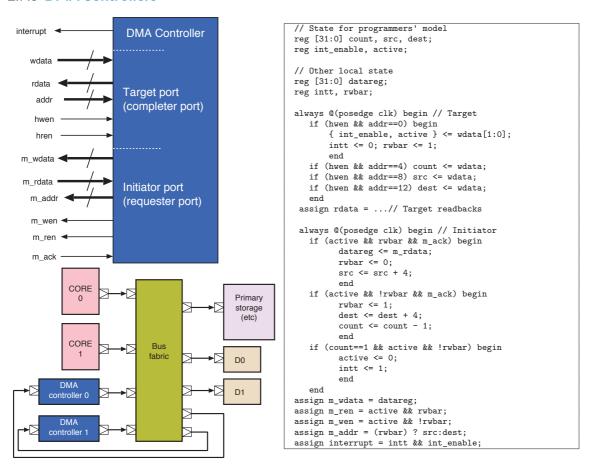

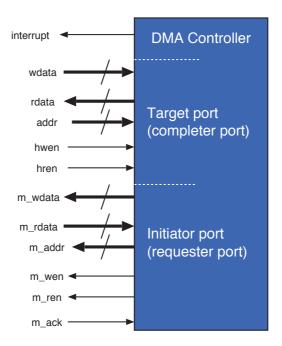

| Figure 2.34 | A simple DMA controller: schematic symbol, example TLM wiring and RTL for one channel                                                                     | 72  |

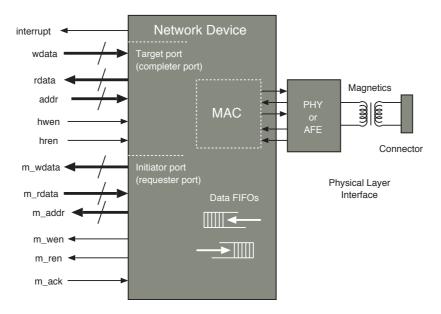

| Figure 2.35 | Net-level schematic symbol for a DMA-capable network interface IP block                                                                                   | 74  |

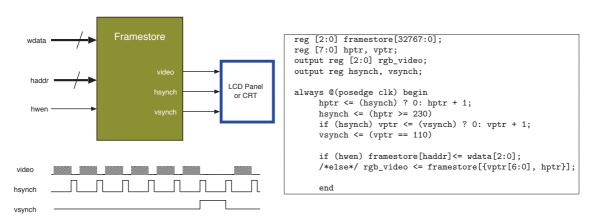

| Figure 2.36 | Structure of a simple frame store, RTL implementation and generated timing waveforms                                                                      | 75  |

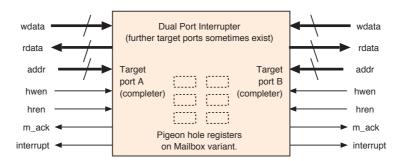

| Figure 2.37 | Doorbell and mailbox block                                                                                                                                | 76  |

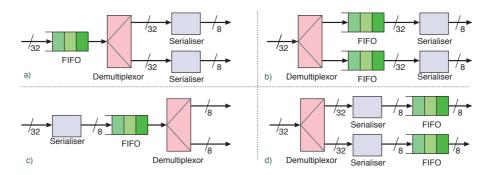

| Figure 3.1  | Four of six permutations that implement a simplex protocol adaptor                                                                                        | 85  |

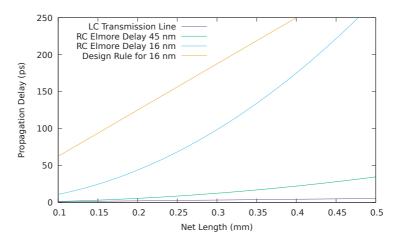

| Figure 3.2  | Comparison of speed-of-light (LC) and RC-based Elmore delay models for propagation along a net. Also shown is a real-world design rule for 16-nm geometry | 88  |

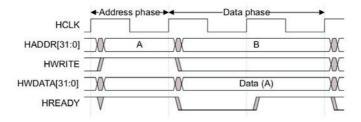

| Figure 3.3  | Timing diagram for AHB bus write cycle with one wait state                                                                                                | 91  |

| Figure 3.4  | Timing diagram for an asynchronous four-phase handshake                                                                                                   | 91  |

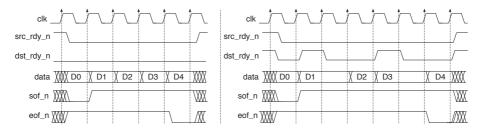

| Figure 3.5  | Timing diagrams for the synchronous LocalLink protocol                                                                                                    | 92  |

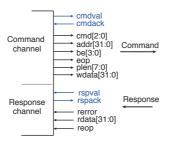

| Figure 3.6  | BVCI core nets                                                                                                                                            | 94  |

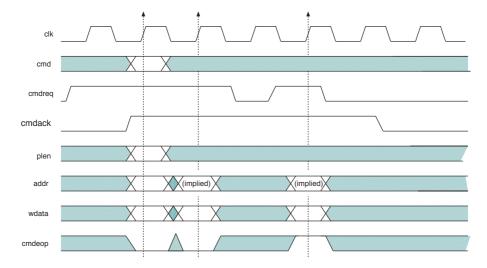

| Figure 3.7  | BVCI protocol: Command phase timing diagram                                                                                                               | 94  |

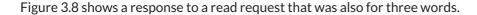

| Figure 3.8  | BVCI protocol: Response phase timing diagram                                                                                                              | 95  |

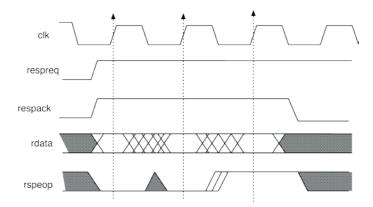

| Figure 3.9  | Out-of-order bus formed from a pair of in-order busses with added tags (blue)                                                                             | 96  |

| Figure 3.10 | Augmenting the tag width through successive multiplexing stages                                                                                           | 96  |

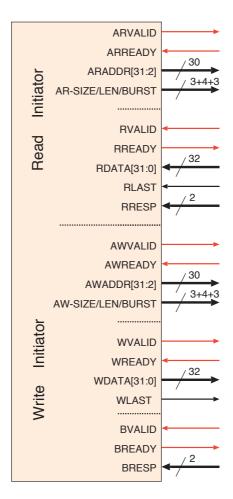

| Figure 3.11 | The baseline port structure for an A32D32 AXI standard initiator showing the five temporally floating channels, two for reads and three for writes        | 98  |

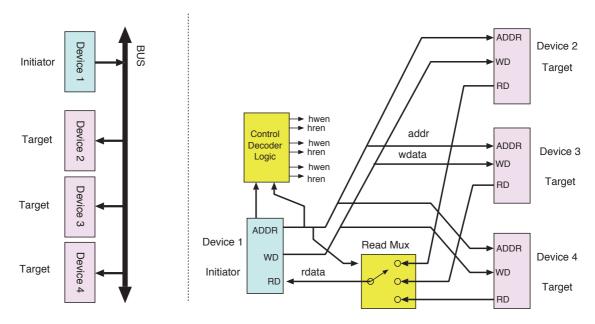

| Figure 3.12 | A basic SoC bus structure for the MSOC1 protocol                                                                                                          | 107 |

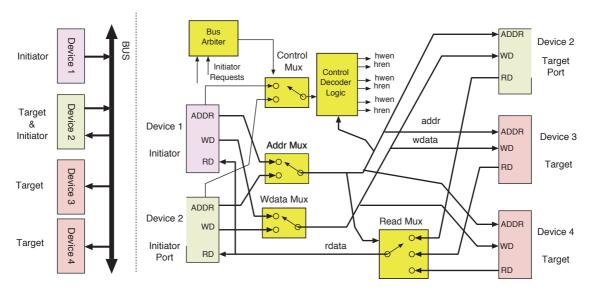

| Figure 3.13 | Example where one of the targets is also an initiator (e.g. a DMA controller)                                                                             | 107 |

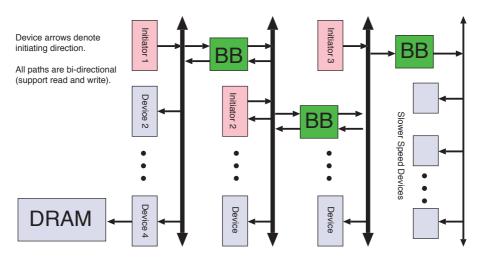

| Figure 3.14 | A system design using three bridged busses                                                                                                                | 108 |

| Figure 3.15 | Bidirectional bus bridge for the MSOC1 protocol                                                                                                           | 109 |

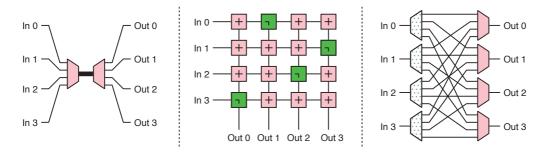

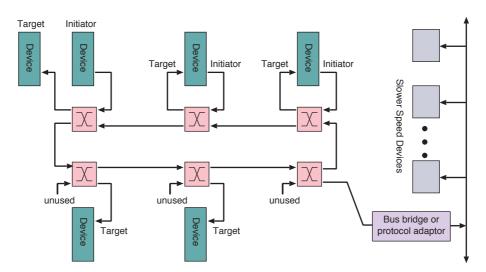

| Figure 3.16 | Crossbar 4 × 4 connectivity implemented in three different ways: with a high-capacity TDM bus (left), crossbar elements (centre) and multiplexors (right) | 110 |

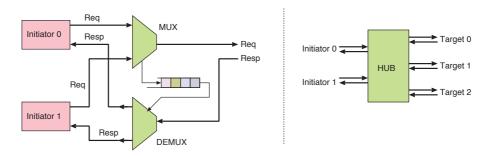

| Figure 3.17 | Multiphase (split transaction) bus demultiplexor and remultiplexor for responses (left)                                                                                                                                                                                                                             | 111 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

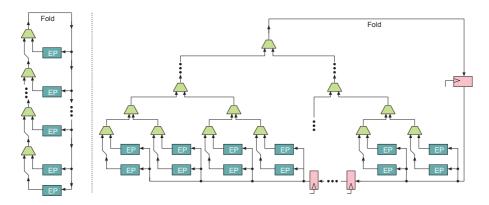

| Figure 3.18 | Two folded busses that have similar component counts                                                                                                                                                                                                                                                                | 113 |

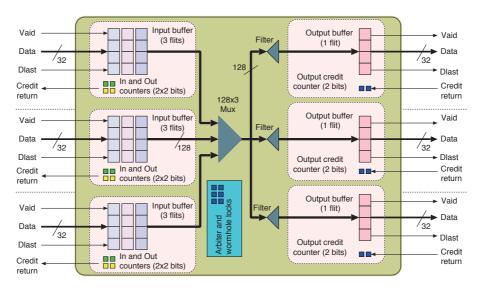

| Figure 3.19 | A radix-3 switching element for a NoC using a broadcast bus at $4\times$ the link bandwidth and credit-based flow control                                                                                                                                                                                           | 114 |

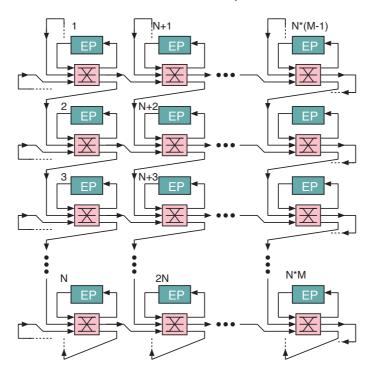

| Figure 3.20 | Example of a NoC fabric using radix-3 switching in a unidirectional torus mesh                                                                                                                                                                                                                                      | 115 |

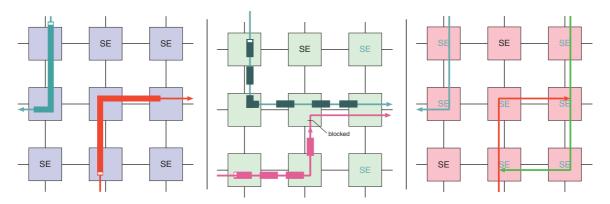

| Figure 3.21 | Illustration of cut-through routing on a 2-D mesh NoC (left), wormhole operation (centre) and potentially deadlocking routes (right)                                                                                                                                                                                | 117 |

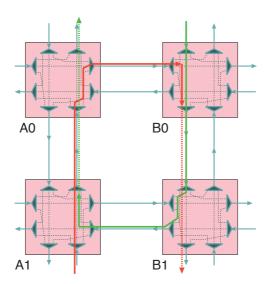

| Figure 3.22 | Four elements in a 2-D mesh                                                                                                                                                                                                                                                                                         | 119 |

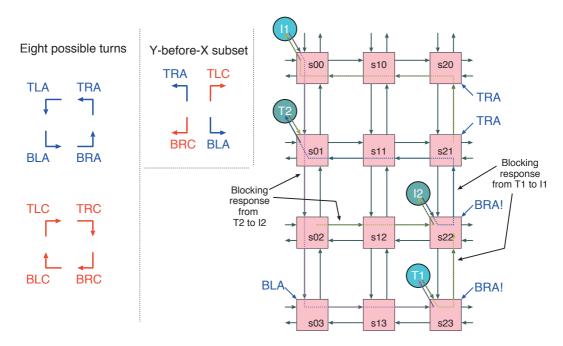

| Figure 3.23 | The eight possible 2-D turns (left), the allowable 2-D turns with Y-before-X (north-south first) routing (centre) and an example set of turns used by two transactions that obey the north-south first global policy but still manage to deadlock owing to interference between requests and responses              | 121 |

| Figure 3.24 | Sample behavioural traffic specification containing a load profile and a transaction phase dependency                                                                                                                                                                                                               | 122 |

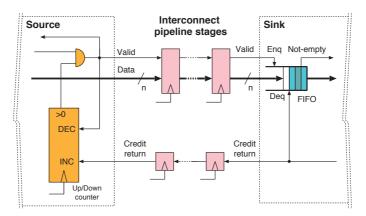

| Figure 3.25 | One possible structure using link-level credit-based flow control, showing tolerance to pipeline stages in the interconnect nets. The forward and return paths need not be matched in delay terms                                                                                                                   | 123 |

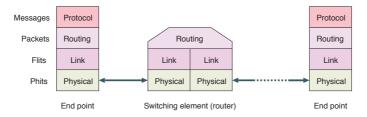

| Figure 3.26 | Two end points interconnected via some number of switching elements                                                                                                                                                                                                                                                 | 124 |

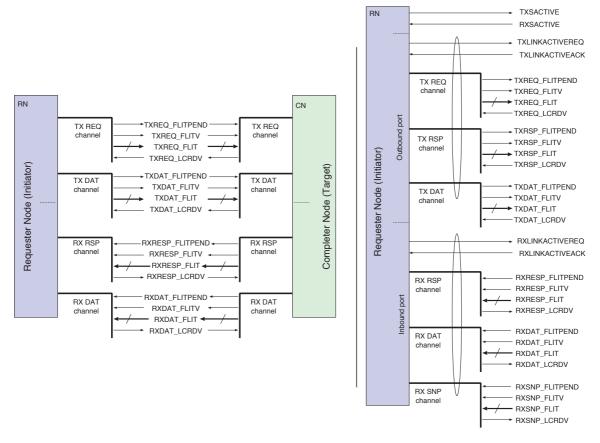

| Figure 3.27 | A minimal application of the AMBA 5 CHI specification between a requester and a completer (left) and full net-level details of the six channels found on a more-typical request node (RN) (right)                                                                                                                   | 125 |

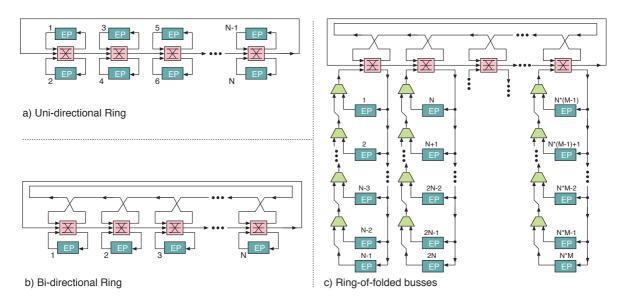

| Figure 3.28 | A ring network                                                                                                                                                                                                                                                                                                      | 129 |

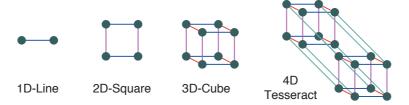

| Figure 3.29 | Regular cubic structures with 1, 2, 3 or 4 dimensions. 5-D and above are hard to draw                                                                                                                                                                                                                               | 131 |

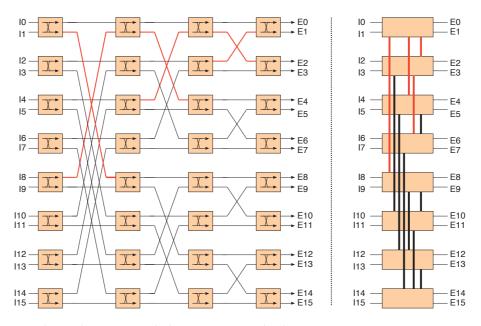

| Figure 3.30 | The butterfly (or shuffle) network topology (left) and a flattened version (right), with some example paths highlighted for comparison                                                                                                                                                                              | 131 |

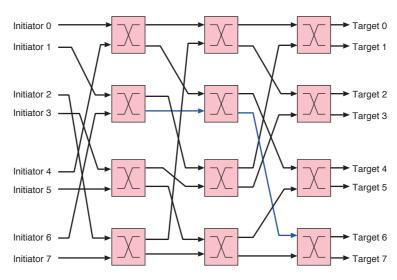

| Figure 3.31 | Example of an $8\times 8$ switching fabric that uses radix-2 elements and the delta wiring pattern                                                                                                                                                                                                                  | 132 |

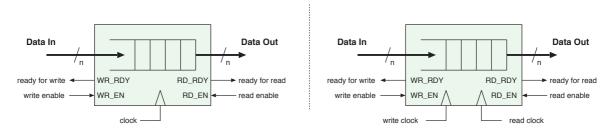

| Figure 3.32 | A one-place pipelined FIFO stage using credit-based flow control                                                                                                                                                                                                                                                    | 135 |

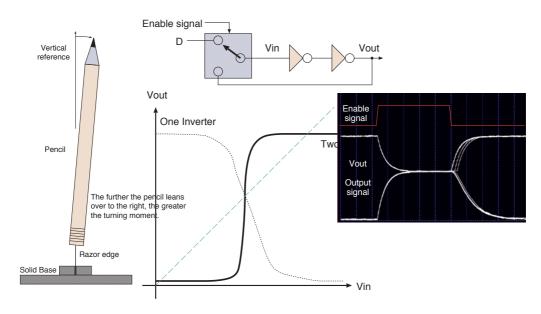

| Figure 3.33 | Metastability illustrated by a pencil balancing on a razor's edge (left). The essential structure of a transparent bistable (latch) and a transfer function (centre). The gate signal and measured responses from a transparent latch with an input wired to a voltage source close to the metastable point (right) | 137 |

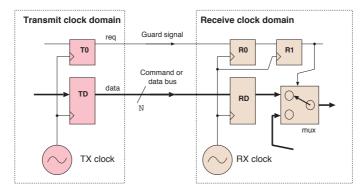

| Figure 3.34 | Generic structure of a simplex CBRI                                                                                                                                                                                                                                                                                 | 138 |

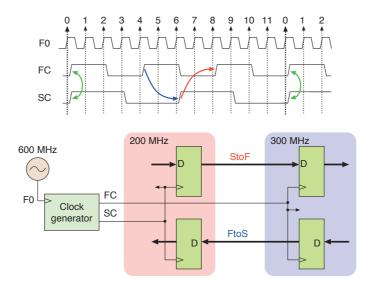

| Figure 3.35 | Timing diagram (top) and a basic structure for two systems that use harmonically locked clocks (bottom)                                                                                           | 140   |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

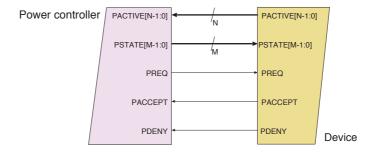

| Figure 3.36 | Net-level view of the AMBA P-channel interface for device power control                                                                                                                           | 141   |

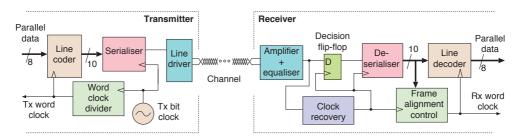

| Figure 3.37 | Main components of an 8b10b, block-coded SERDES (serialiser/deserialiser) transceiver (transmitter/receiver) operating over a twisted-pair channel                                                | 142   |

| Figure 4.1  | Example of parallel speedup                                                                                                                                                                       | 156   |

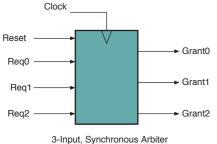

| Figure 4.2  | A schematic of a typical arbiter (left) and the RTL implementation (right) for a three-port synchronous example using static priority with pre-emption. See also Figure 6.31                      | 159   |

| Figure 4.3  | General structure of a queue/server pair with mean customer rate $\lambda$ and mean service rate $\mu$                                                                                            | 160   |

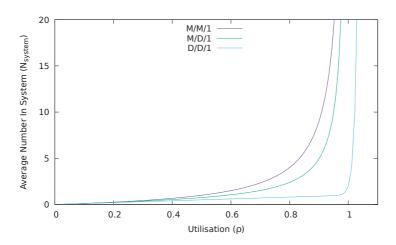

| Figure 4.4  | Plots of the average number of customers in a system versus the utilisation $\rho$ for three common arrival/service disciplines                                                                   | 161   |

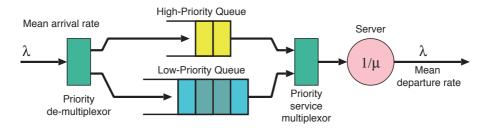

| Figure 4.5  | Separate queueing for high-priority and low-priority traffic gives an expedited service                                                                                                           | 163   |

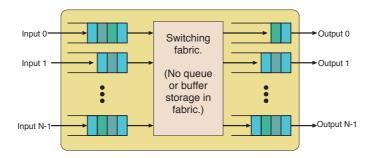

| Figure 4.6  | Generic switch that includes both input and output buffering on the input and output ports, respectively, of a buffer-less switch fabric                                                          | 164   |

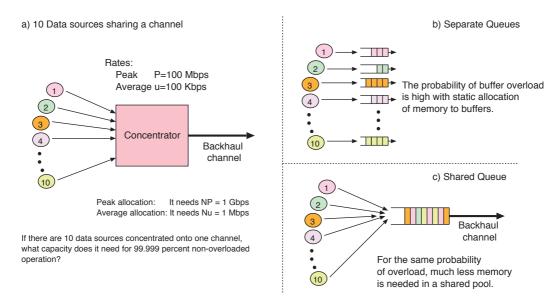

| Figure 4.7  | Two scenarios that demonstrate statistical multiplexing gain for $N=10$ sources                                                                                                                   | 165   |

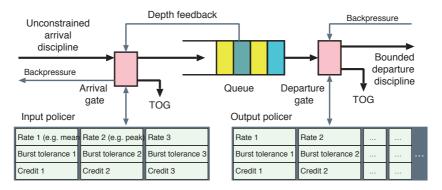

| Figure 4.8  | A policed queue showing both input and output regulators, although commonly only one site would be policed                                                                                        | 167   |

| Figure 4.9  | Essence of a software implementation for one channel of a generic traffic policer or regulator                                                                                                    | 167   |

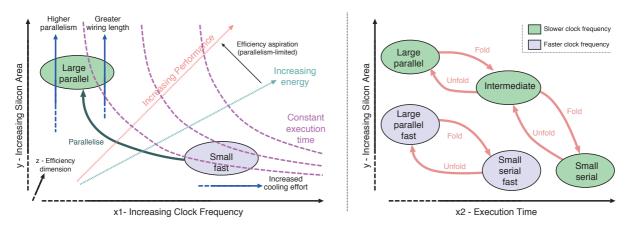

| Figure 4.10 | Abstract views of the principal axes that span the SoC design space for a task                                                                                                                    | 168   |

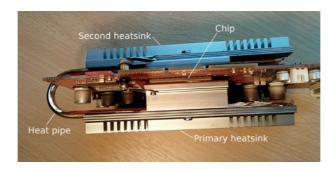

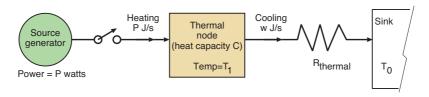

| Figure 4.11 | Thermal management of a high-power chip                                                                                                                                                           | 169   |

| Figure 4.12 | Generic thermal circuit, showing on/off heat source, thermal node and thermal resistance between the node and its heat sink                                                                       | 169   |

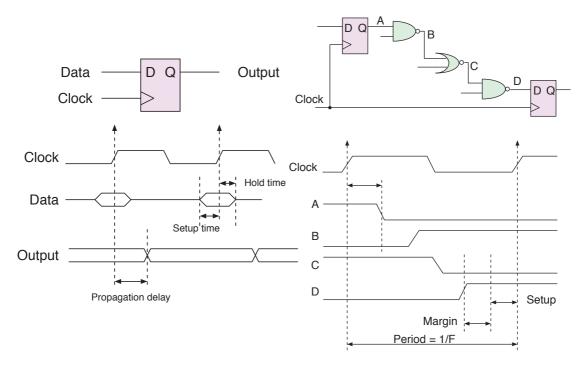

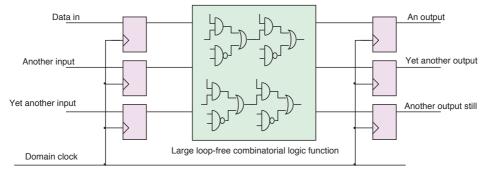

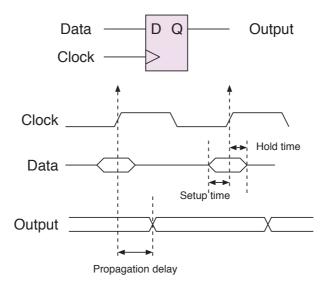

| Figure 4.13 | Primary timing characteristics of a D-type flip-flop (left). Typical nature of a critical path in a synchronous clock domain indicating how the maximum clock frequency (F) is calculated (right) | 172   |

| Figure 4.14 | A circuit before (top) and after (bottom) insertion of an additional pipeline stage                                                                                                               | 173   |

| Figure 4.15 | Flip-flop migration                                                                                                                                                                               | 173   |

| Figure 4.16 | Schematic and count sequence for a divide-by-five counter using Johnson encoding                                                                                                                  | g 175 |

| Figure 4.17 | Two code fragments using message-passing in shared memory with explicit memory fences                                                                                                             | 176   |

| Figure 4.18 | SRAM memory bank structures for MCMs (top) with two interconnection patterns inside the SoC (bottom)                                              | 177    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Figure 4.19 | Pseudo-dual porting of RAM (using write mirroring)                                                                                                | 178    |

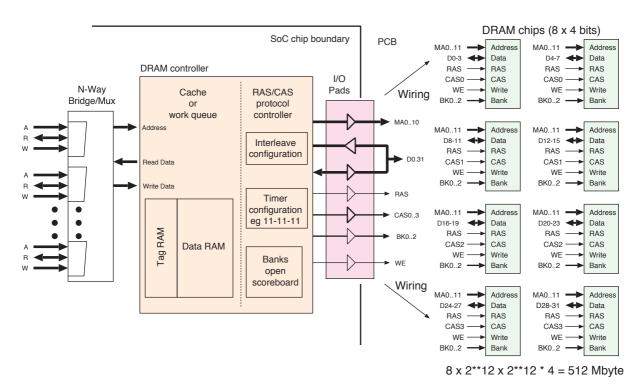

| Figure 4.20 | Typical structure of a 32-bit DRAM controller connected to DRAM devices                                                                           | 180    |

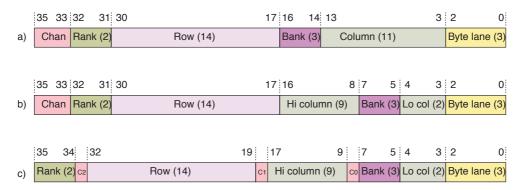

| Figure 4.21 | Three possible arrangements of DRAM address fields within a physical address                                                                      | 181    |

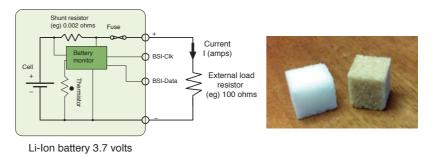

| Figure 4.22 | (a) Lithium-ion battery for a mobile phone (3.7 V, 1650 mA h, 6 W h or 22 kJ), external view. (b) Typical internal structure. (c) Two sugar cubes | 183    |

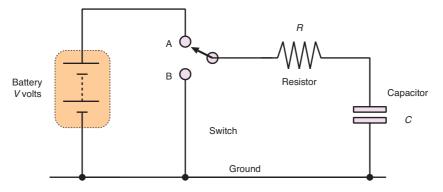

| Figure 4.23 | Lumped-element electrical equivalent modelling of dynamic power use of a CMOS SoC                                                                 | 184    |

| Figure 4.24 | A generic CMOS invertor structure shown with explicit parasitic resistances and lumped-equivalent output loading                                  | 184    |

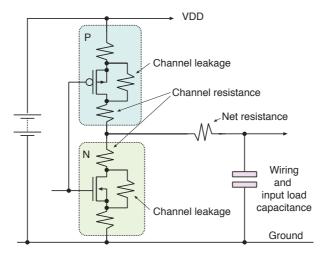

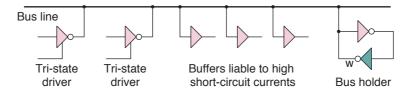

| Figure 4.25 | A tri-state data line showing driving gates, sensing buffers and a bus holder (or keeper)                                                         | 185    |

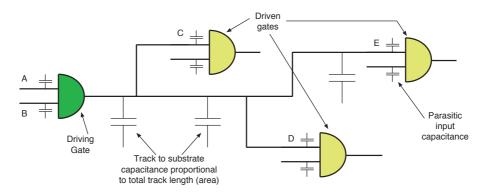

| Figure 4.26 | Logic net with a single source and three loads, showing tracking and input load capacitances                                                      | 187    |

| Figure 4.27 | Dynamic energy use for various technologies                                                                                                       | 189    |

| Figure 4.28 | Fanout 4 (FO4) delay specification (left) and CMOS logic propagation delay versus supply voltage (right)                                          | 190    |

| Figure 4.29 | SPICE description and setup for two transistors arranged as a CMOS invertor simulated with a two-step input                                       | 192    |

| Figure 4.30 | Plots of the invertor when running from $V_{CC}$ supplies of 2.5 V (left) and 1.5 V (right                                                        | t) 193 |

| Figure 4.31 | Clock enable using (a) a multiplexer, (b) an AND gate and (c) an OR gate                                                                          | 195    |

| Figure 4.32 | Illustrating a transparent latch and its use to suppress clock gating glitches                                                                    | 195    |

| Figure 4.33 | Using XOR gates to determine whether a clock edge would have any effect                                                                           | 196    |

| Figure 4.34 | Clock-needed computations forwarded down a pipeline                                                                                               | 196    |

| Figure 4.35 | Power gating in general (left) and an actual power gate circuit (right)                                                                           | 197    |

| Figure 4.36 | Debugging hardware for a single-core SoC                                                                                                          | 202    |

| Figure 4.37 | Typical additional event-stream debug resources for a modern MPSoC                                                                                | 203    |

| Figure 4.38 | JTAG interface chaining at board level to create a top-level node in the debug device tree                                                        | 205    |

| Figure 4.39 | Basic structure of the additional logic required in input and output pads for boundary scanning                                                   | 206    |

| Figure 4.40 | A static RAM with self-test wrapper around it                                                                                                     | 207    |

| Figure 4.41 | Crystal oscillator circuit (left), canned crystal and contents (centre), and specification and output waveform (right)                                                                            | 212 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.42 | Clock multiplication using a PLL (left) and clock distribution layout using a fractal H-tree (right)                                                                                              | 212 |

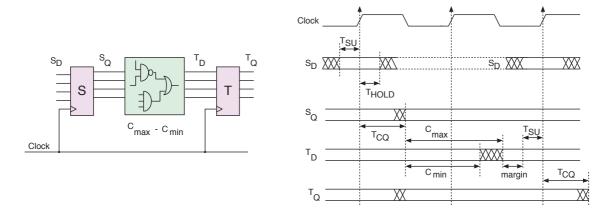

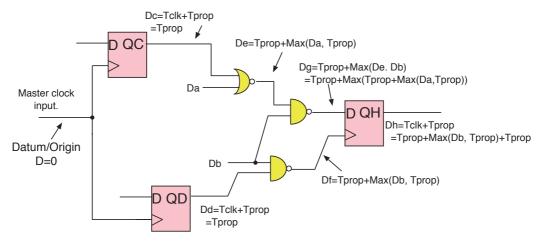

| Figure 4.43 | Clock skewing                                                                                                                                                                                     | 214 |

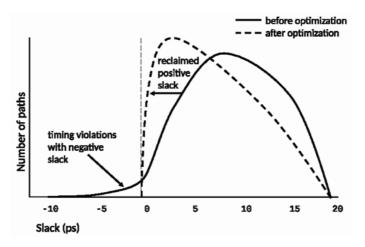

| Figure 4.44 | Basic form of a timing slack graph                                                                                                                                                                | 215 |

| Figure 4.45 | Schematic (left) and timing diagram (right) of a typical multi-cycle path                                                                                                                         | 215 |

| Figure 5.1  | Overall setup of a generic ESL flow                                                                                                                                                               | 224 |

| Figure 5.2  | A 10-bit binary counter with synchronous reset, coded as a SystemC class                                                                                                                          | 229 |

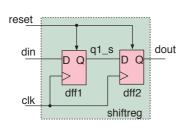

| Figure 5.3  | Schematic (left) and SystemC structural netlist (right) for a 2-bit shift register                                                                                                                | 230 |

| Figure 5.4  | Compute/commit behaviour                                                                                                                                                                          | 230 |

| Figure 5.5  | Sample code using SC_THREAD                                                                                                                                                                       | 231 |

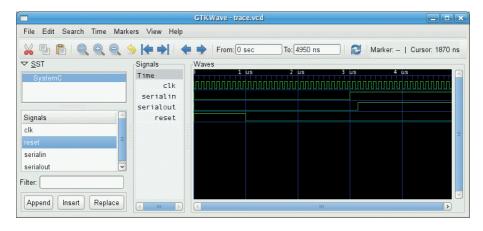

| Figure 5.6  | An example waveform view plotted by gtkwave                                                                                                                                                       | 232 |

| Figure 5.7  | Naming nets                                                                                                                                                                                       | 233 |

| Figure 5.8  | Equality operator overload                                                                                                                                                                        | 233 |

| Figure 5.9  | Positive edge                                                                                                                                                                                     | 234 |

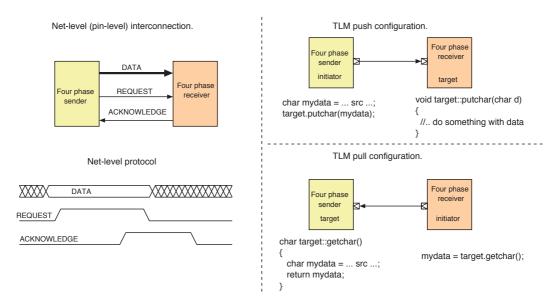

| Figure 5.10 | Three views of the four-phase transactional protocol from Section 3.1.3 operating between a sender and a receiver                                                                                 | 235 |

| Figure 5.11 | Schematic of a FIFO device (top) and its typical instantiation (bottom)                                                                                                                           | 236 |

| Figure 5.12 | SystemC module definition of an interface (left) and FIFO writer (right)                                                                                                                          | 236 |

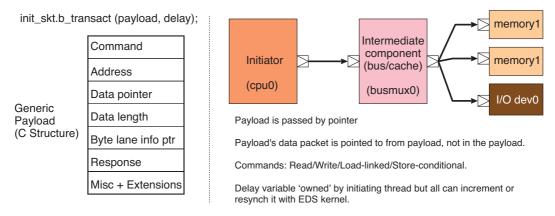

| Figure 5.13 | TLM 2.0 generic payload structure (left) and interconnection of three IP blocks showing passthrough and demultiplexing (right)                                                                    | 238 |

| Figure 5.14 | Setting up a generic payload                                                                                                                                                                      | 238 |

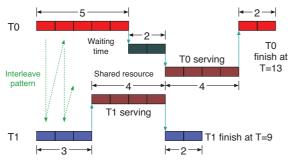

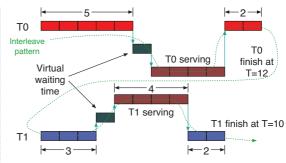

| Figure 5.15 | Illustration of modelling artefacts relating to model interleaving and timing arising from loosely timed TLM                                                                                      | 243 |

| Figure 5.16 | Essence of the code for a virtual queue contention point                                                                                                                                          | 245 |

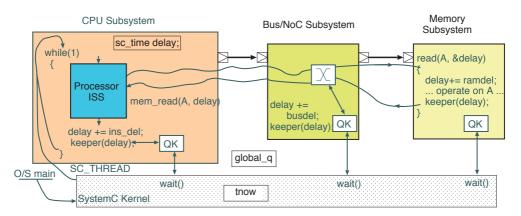

| Figure 5.17 | Typical setup of a thread using loosely timed modelling with a quantum keeper for one core of an MPSoC                                                                                            | 246 |

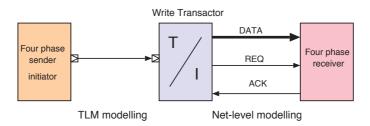

| Figure 5.18 | Mixing modelling styles using a target-to-initiator transactor                                                                                                                                    | 247 |

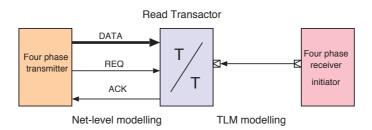

| Figure 5.19 | Mixing modelling styles using a mailbox paradigm transactor                                                                                                                                       | 247 |

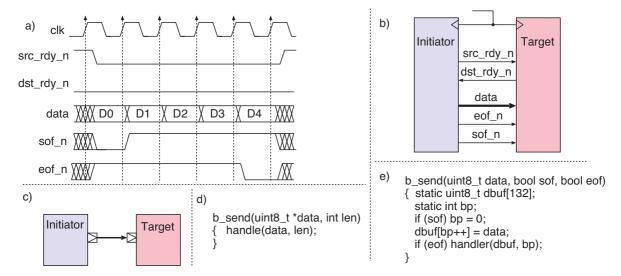

| Figure 5.20 | Five views of the LocalLink protocol (also of AXI4-Stream). (a) Timing diagram. (b) Net-level wiring. (c) TLM abstract view. (d) Blocking TLM target code, big step. (e) Blocking TLM, small step | 248 |

| Figure 5.21 | Main step function                                                                                                                                                                                                                                                                                | 250 |